# 修士論文 HL-LHC 実験に向けたピクセル検出器の試験量産の結果解析 および本量産のための改善

早稲田大学 先進理工学研究科 物理学及応用物理学専攻 寄田研究室 小川貴弘

2025年3月3日

現在、欧州原子核研究機構 (CERN) では、標準模型の検証や標準模型を超えた新物理の探索を目的とした素粒子実験として、LHC-ATLAS 実験が進行中である。この実験では、Large Hadron Collider(LHC) と呼ばれる陽子陽子衝突型円形加速器と、ATLAS と呼ばれる汎用検出器が用いられている。LHC は、ジュネーヴ郊外の地下 100 m に存在する一周 27 km の加速器であり、重心系エネルギーを 13.6 TeV として稼働している。また、ATLAS は、LHC の衝突点に位置する検出器として、荷電粒子の飛跡再構成による運動量測定等を行っている。この LHC-ATLAS 実験は、2020 年代後半にかけて HL-LHC 実験へのアップグレードが計画されている。HL-LHC 実験への増強を行うことにより、実験における瞬間、積分ルミノシティや粒子衝突頻度等の増加を図り、さらに多くのデータ統計を得られるようにすることで効率的な新物理探究への貢献を目指している。この改良に伴い、積分ルミノシティは約 10 倍、瞬間ルミノシティやバンチ衝突頻度も数倍ほど増加することから、検出器への放射線損傷の深刻化が想定される。現行の内部飛跡検出器では、想定される放射線損傷に耐えられないと予想されるため、ITk(Inner Tracker)と呼ばれるシリコン半導体検出器を代わりに実装する計画が進行中である。

ITk とは、シリコンセンサーを用いた半導体検出器である。ITk には、ピクセル検出器とストリップ検出器の2種類が存在し、本論文ではピクセル検出器について扱う。HL-LHC 実験において、現行の内部飛跡検出器と交換されるため、世界中で約10000台のモジュールの量産が計画されており、日本では約3000台を量産することが決まっている。2023年6月から試験量産が始まり約150台が製造された。2024年10月からは本格的な量産が始まり、HL-LHC 実験に向けてモジュールの製造を行っている。このITk の量産においては、モジュールの組み立てや品質管理試験が必要となる。本研究では、品質管理試験の一つである電気回路読み出し試験の結果解析を行い、本量産に向けた試験の改善を目指した。

ITk ピクセルモジュールの品質管理試験においては、電気回路読み出し試験が試験量産および本量産で行われている。この試験では、約70個のパラメータを調べている。手法としては、各量産において得られた結果をまとめ、読み出し試験を行う各パラメータについて、時系列での傾向や基準値外の結果を出力した検出器の割合などをそれぞれ確認するという形で結果解析を進めた。品質管理試験の結果が保存された LocalDB と呼ばれるデータベースから各試験の値を取り出し、プロットの作成等を行うことで試験結果をまとめた。

解析の結果として、70 個ほどあるパラメータのうち、約50 個のパラメータにおいて、基準値を外れたチップが全体の10% 以上を占めていることが分かった。特に、検出器回路に電源電圧を供給している機器の動作確認を行っている SLDO 試験では、試験量産、本量産ともに基準値外の検出器が全体の $30\sim60\%$  を占めるパラメータが確認された。また、試験量産の結果から、試験に不合格であったチップが他のチップに悪影響を及ぼしている可能性について調べた。加えて、あるパラメータにおいて基準値外の値を出力したチップが、他のパラメータにおいてどういった結果を出力しているかを調べ、あるチップがそのパラメータで問題ありと判断された場合に、そのチップが他のパラメータでも基準値外の結果を出力しやすいようなパラメータの有無を調べた。

今後の展望としては、解析を行った試験結果をもとに、基準値内の結果を出力した検出器の割合が多いパラメータとそうでないパラメータを分類し、それぞれの結果の原因についてより詳細な考察を行う。また、現在の試験で用いられている基準値や試験方法が妥当であるか否かを検証することで、どうすれば本量産において高品質の製造を行えるかについても同様に考察を行う。

目次

# 目次

| 1 |       | LHC-ATLAS 実験               | 7  |

|---|-------|----------------------------|----|

|   | 1.1   | LHC                        | 7  |

|   | 1.2   | ATLAS 検出器                  | 7  |

|   | 1.2.  | 1 内部飛跡検出器                  | 8  |

|   | 1.2.  | 2 カロリメータ                   | 11 |

|   | 1.2.  | 3 ミューオン検出器                 | 12 |

|   | 1.3   | トリガーシステム                   | 12 |

| 2 |       | HL-LHC 実験                  | 13 |

|   | 2.1   | 検出器のアップグレード                | 14 |

| 3 |       | ITk(Inner Tracker)         | 15 |

|   | 3.1   | 半導体検出器                     | 16 |

|   | 3.1.  | 1 半導体                      | 16 |

|   | 3.1.  | 2 半導体の種類                   | 17 |

|   | 3.1.  | 3 pn 接合による荷電粒子の検出          | 17 |

|   | 3.1.  | 4 放射線損傷                    | 18 |

|   | 3.2   | シリコンピクセルセンサー               | 18 |

|   | 3.3   | FE チップ (Front-End IC chip) | 21 |

|   | 3.4   | フレキシブル基板                   | 21 |

|   | 3.5   | ピクセル Quad モジュール            | 21 |

| 4 |       | プロダクション                    | 23 |

|   | 4.1   | 日本におけるプロダクション              | 24 |

|   | 4.2   | ハヤシレピックの生産体制               | 24 |

| 5 |       | ITk モジュールの量産               | 31 |

|   | 5.1   | モジュールのアセンブリ                | 32 |

|   | 5.2   | ワイヤボンディング                  | 33 |

|   | 5.3   | パリレンコーティング                 | 34 |

|   | 5.4   | ワイヤボンドプロテクション              | 34 |

|   | 5.5   | 耐久試験                       | 35 |

|   | 5.6   | モジュールの品質管理試験               | 35 |

|   | 5.6.  | 1 質量測定 (Mass Measurement)  | 35 |

|   | 5.6.  | 2 外観測定 (Visual Inspection) | 35 |

|   | 5.6.  | 3 サイズ測定 (Metrology)        | 37 |

|   | 5.6.4 | 4 電気回路読み出し試験               | 37 |

| 目次  | 月                | 次  |

|-----|------------------|----|

| 6   | ITk モジュールの試験結果解析 | 37 |

| 6.1 | 電気回路読み出し試験       | 37 |

| 6.1 | 1 接続の確認          | 37 |

| 6.1 | 2 IV scan        | 37 |

| 6.1 | 3 simple scan    | 37 |

| 6.1 | 4 YARR scan      | 43 |

| 6.2 | 電気回路読み出し試験の結果解析  | 53 |

| 6.3 | パラメータの分類         | 69 |

| 6.4 | fail チップの原因      | 71 |

| 7   | まとめと展望           | 79 |

| 8   | 考察               | 80 |

図目次

# 図目次

| 1.1  | LHC 概略図 [1]                                 | 7  |

|------|---------------------------------------------|----|

| 1.2  | ATLAS 検出器の概観図 [2]                           | 8  |

| 1.3  | 内部飛跡検出器の概観図 [3]                             | 10 |

| 1.4  | 内部飛跡検出器断面図 [4]                              | 10 |

| 1.5  | カロリメータの概観図 [5]                              | 11 |

| 1.6  | ミューオン検出器の概観図 [6]                            | 12 |

| 1.7  | トリガーシステムの概要図 [7]                            | 13 |

| 2.1  | ITk 検出器予想図 [8]                              | 14 |

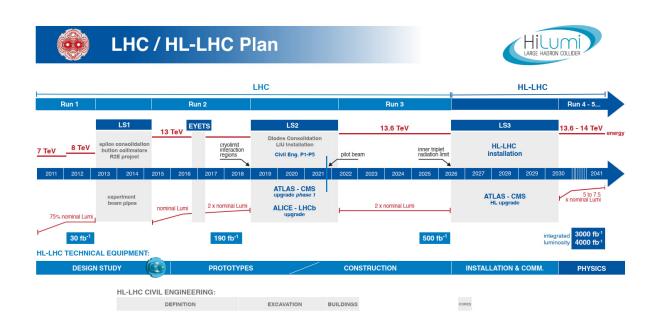

| 2.2  | HL-LHC 計画 [9]                               | 15 |

| 3.1  | ITk 検出器ビームライン方向断面図 [10]                     | 16 |

| 3.2  | インナーシステム [11]                               | 18 |

| 3.3  | エンドキャップ [11]                                | 19 |

| 3.4  | アウターバレル $[11]$                              | 19 |

| 3.5  | (左)3D センサーのイメージ図 (右) プラナーセンサーのイメージ図 [12]    | 20 |

| 3.6  | $n^+-in-p$ 型センサーのイメージ図                      | 20 |

| 3.7  | ITk ピクセルモジュールの FE チップの動作のイメージ図              | 21 |

| 3.8  | ITk ピクセル Quad モジュール [11]                    | 22 |

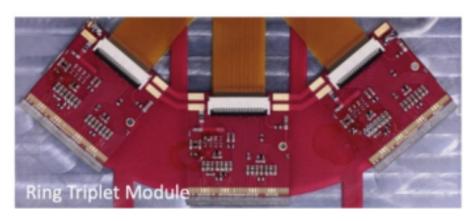

| 3.9  | ITk ピクセル Triplet モジュール [13]                 | 22 |

| 3.10 | ITk モジュール実装後の検出器断面図 [14]                    | 23 |

| 3.11 | ITk モジュールの構成イメージ図                           | 23 |

| 4.1  | ハヤシレピックの量産サイトの様子                            | 25 |

| 4.2  | クーリングボックスの外観図                               | 26 |

| 4.3  | クーリングボックス内部の様子                              | 26 |

| 4.4  | クーリングボックス内部の構成 [15]                         | 27 |

| 4.5  | Grafana の表示                                 | 27 |

| 4.6  | X 線装置の外観図                                   | 28 |

| 4.7  | 恒温槽の外観図.................................... | 29 |

| 4.8  | 外観測定用顕微鏡の外観図                                | 30 |

| 4.9  | デシケータの外観図                                   | 31 |

| 5.1  | モジュールの組み立てや品質管理試験の流れ                        | 32 |

| 5.2  | (左) ベアモジュール用治具 (右) フレキシブル基板用治具 $[16]$       | 32 |

| 5.3  | ワイヤーボンダーの外観図 $[16]$                         | 33 |

| 5.4  | パリレンコーティングの様子                               | 34 |

| 5.5  | ワイヤボンドプロテクション取り付け後のモジュールの外観図 [17]           | 35 |

| 5.6  | 外観検査に用いられる画像の例                              | 36 |

| 5.7  | 外観検査のイメージ図 [18]                             | 36 |

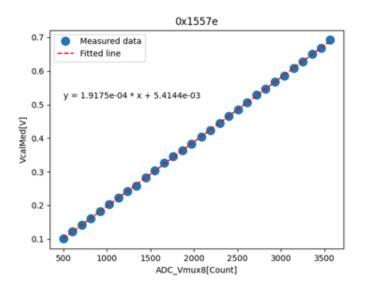

| 6.1  | ADC calibration の試験結果の例 [17]                | 38 |

図目次

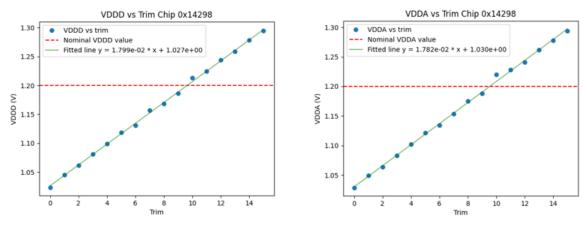

| 6.2  | VDDA/D と trim の関係測定の結果の例 [17]                                | 39 |

|------|--------------------------------------------------------------|----|

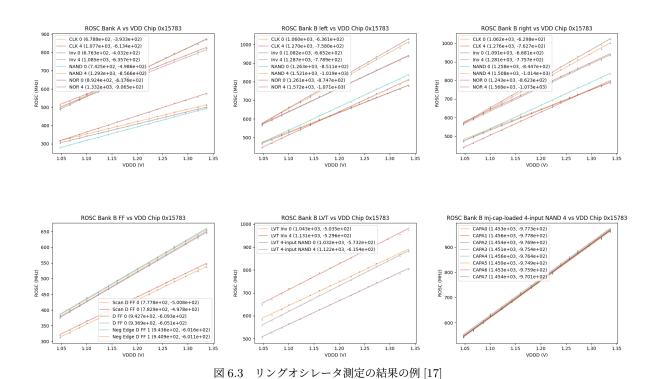

| 6.3  | リングオシレータ測定の結果の例 [17]                                         | 39 |

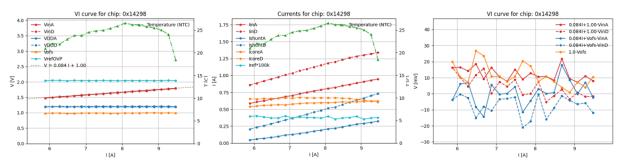

| 6.4  | SLDO の結果の例 [17]                                              | 40 |

| 6.5  | SLDO レギュレータの回路図 [17]                                         | 41 |

| 6.6  | SLDO レギュレータの出力 [17]                                          | 41 |

| 6.7  | Vcal calibration の試験結果の例 [17]                                | 42 |

| 6.8  | Digital Scan の試験結果の例 [17]                                    | 44 |

| 6.9  | Analog Scan の試験結果の例 [17]                                     | 45 |

| 6.10 | Tuning 前の Threshold scan の試験結果の例 [17]                        | 45 |

| 6.11 | Tuning 後の Threshold scan の試験結果の例 [17]                        | 46 |

| 6.12 | 試験量産での TOT scan の試験結果の例 [17]                                 | 46 |

| 6.13 | 本量産での TOT scan の試験結果の例 [17]                                  | 47 |

| 6.14 | Global threshold (re-)tune の試験結果の例 [17]                      | 48 |

| 6.15 | Pixel threshold (re-)tune の試験結果の例 [17]                       | 49 |

| 6.16 | TOT tune の試験結果の例 [17]                                        | 50 |

| 6.17 | Noise scan の試験結果の例 [17]                                      | 50 |

| 6.18 | Disconnected bump scan の試験結果の例 [17]                          | 51 |

| 6.19 | Merged bump scan の試験結果の例 [17]                                | 52 |

| 6.20 | Zero-bias threshold scan の試験結果の例 [17]                        | 52 |

| 6.21 | Xray scan の試験結果の例 [17]                                       |    |

| 6.22 | 電気回路読み出し試験結果の例・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・           | 53 |

| 6.23 | FE チップの読み出し試験結果の定義                                           | 54 |

| 6.24 | 試験量産での Initial stage における pass チップ、fail チップの割合               | 56 |

| 6.25 | 試験量産での Final stage における pass チップ、fail チップの割合                 | 58 |

| 6.26 | 本量産での Initial stage における pass チップ、fail チップの割合                | 61 |

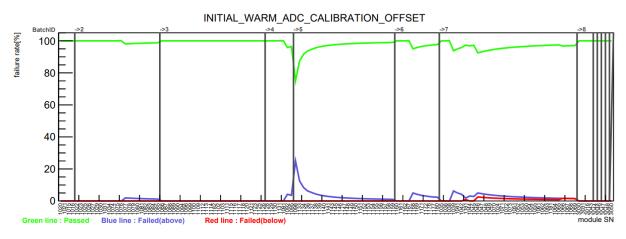

| 6.27 | ADC CALIBRATION OFFSET の pass チップ、fail チップの時系列変化             |    |

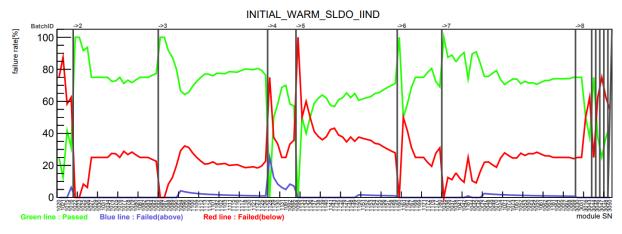

| 6.28 | SLDO IIND の pass チップ、fail チップの時系列変化                          | 62 |

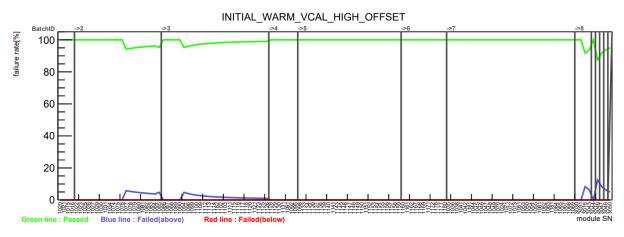

| 6.29 | VCAL HIGH OFFSET の pass チップ、fail チップの時系列変化                   | 63 |

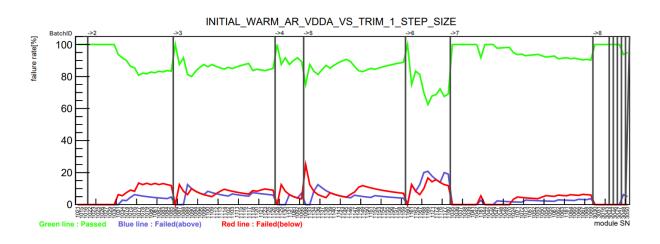

| 6.30 | AR VDDA VS TRIM STEP SIZE の DAC 値ごとの pass チップ、fail チップの時系列変化 | 64 |

| 6.31 | LP VOFFS の pass チップ、fail チップの時系列変化                           | 64 |

| 6.32 | 試験量産での Initial stage における各チップの割合 (上) 基準値変更前 (下) 基準値変更後 .     | 66 |

| 6.33 | 試験量産での Final stage における各チップの割合 (上) 基準値変更前 (下) 基準値変更後         | 67 |

| 6.34 | 本量産での Initial stage における各チップの割合 (上) 基準値変更前 (下) 基準値変更後        | 68 |

| 6.35 | 試験量産の Initial stage での SLDO VDDA、VDDD の試験結果 (上) 基準値変更前 (下)   |    |

|      | 基準値変更後                                                       | 68 |

| 6.36 | 試験量産の Initial stage での SLDO IINA、IIND の試験結果 (上) 基準値変更前 (下)基準 |    |

|      | 値変更後                                                         | 69 |

| 6.37 | モジュール番号 20UPGM22601096 のチップごとの試験結果 (左)Initial stage (右)Final |    |

| •    | stage                                                        | 72 |

| 6.38 | モジュール番号 20UPGM22601099 のチップごとの試験結果 (左)Initial stage (右)Final                                                                            |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|----|

|      | stage                                                                                                                                   | 72 |

| 6.39 | モジュール番号 20UPGM22601027 のチップごとの試験結果 (左)Initial stage (右)Final                                                                            |    |

|      | stage                                                                                                                                   | 72 |

| 6.40 | 試験量産での SLDO と ADC calibration における fail チップ相関 (上)Initial stage                                                                          |    |

|      | $(\top) Final\ stage \dots \dots$ | 74 |

| 6.41 | 試験量産での SLDO の各パラメータにおける fail チップ相関 (上)Initial stage (下)Final                                                                            |    |

|      | stage                                                                                                                                   | 75 |

| 6.42 | 試験量産での SLDO と Analog readback における fail チップ相関 (上)Initial stage                                                                          |    |

|      | $(\top) Final\ stage \dots \dots$ | 76 |

| 6.43 | 試験量産での SLDO と Vcal calibration における fail チップ相関 (上)Initial stage (下)Fi-                                                                  |    |

|      | nal stage                                                                                                                               | 77 |

| 6.44 | 試験量産での SLDO と LP mode における fail チップ相関 (上)Initial stage (下)Final stage                                                                   | 78 |

表目次

# 表目次

| 2.1 | LHC と HL-LHC のパラメータ比較                 | 14 |

|-----|---------------------------------------|----|

| 3.1 | ITk ピクセルモジュールの性能                      | 16 |

| 3.2 | ITK 各層で用いられるセンサーやモジュールの詳細             | 23 |

| 5.1 | Araldite2011 の物性値                     | 33 |

| 6.1 | 変更前後の SLDO パラメータの基準値                  | 65 |

| 6.2 | 現在、電気回路読み出し試験において試験結果の解析をしているパラメータの一覧 | 70 |

| 6.3 | fail チップの割合によるパラメータの分類                | 71 |

# 1 LHC-ATLAS 実験

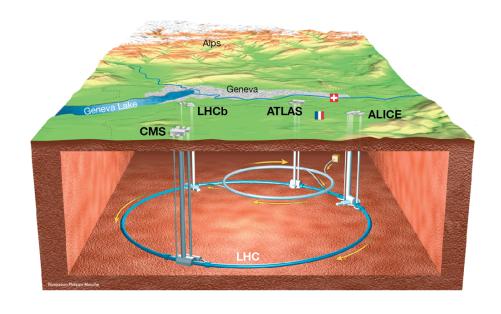

## 1.1 LHC

Large Hadron Collider(LHC) は、欧州原子核研究機構(CERN)によって建設された、スイスのジュネーヴ郊外に存在する陽子陽子衝突型円形加速器であり、地下  $100~\mathrm{m}$  に位置する一周約  $27~\mathrm{km}$  の加速器である。図  $1.1~\mathrm{tk}$  、LHC の概略図である。LHC-ATLAS 実験は、陽子同士を光速近くまで加速、衝突させることによって発生する粒子の振る舞いを調べることで、標準模型の検証や新物理探索を行うことを目的とした素粒子実験である。現在、LHC では、超伝導磁石によってまとめられた約  $10^{11}$  個の陽子をまとめたバンチを約  $7~\mathrm{TeV}$  まで加速して衝突させる形で運用されている。重心系エネルギーを  $13.6~\mathrm{TeV}$ 、瞬間ルミノシティを  $2.0~\mathrm{tk}$  ×  $10^{34}~\mathrm{cm}^{-2}\mathrm{s}^{-1}$  として運転が行われている。また、LHC-ATLAS 実験は、 $2020~\mathrm{tk}$  年代後半にかけて瞬間ルミノシティを  $5.0~7.5~\mathrm{tk}$   $10^{34}~\mathrm{cm}^{-2}\mathrm{s}^{-1}$  まで増加させた高輝度 LHC(High Luminosity LHC: HL-LHC) 実験へのアップグレードが予定されている。HL-LHC 実験は、加速器や検出器のアップグレードによって、積分ルミノシティを約  $10~\mathrm{tk}$  倍まで増やし、新粒子の探索感度の上昇やヒッグス粒子に関する研究のさらなる発展を目指している。そのため、これまでの Run の知見を活かして、HL-LHC 実験において実装予定の検出器の安定した生産やその品質管理が非常に重要となっている。それに伴い、日本も含め ATLAS 実験に参加している各国は、検出器モジュールの量産体制の構築を行っている。

図 1.1 LHC 概略図 [1]

# 1.2 ATLAS 検出器

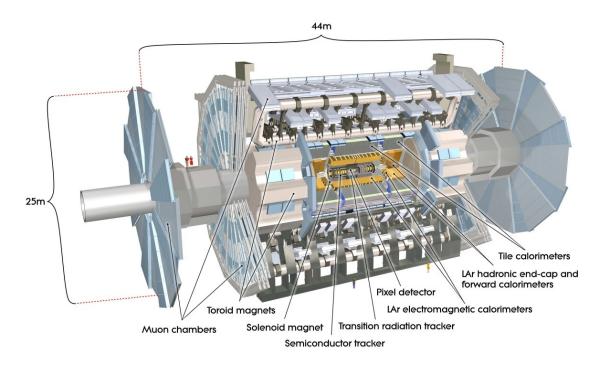

ATLAS 検出器とは、LHC-ATLAS 実験にて用いられている汎用検出器である。全長  $45~\mathrm{m}$ 、直径  $25~\mathrm{m}$ 、重  $2~\mathrm{m}$   $2~\mathrm{m}$  2

を中心として、内部飛跡検出器、カロリメータ、ミューオン検出器によって構成されている。内部飛跡検出器は荷電粒子の飛跡測定、カロリメータでは電子などの粒子のエネルギー測定、ミューオン検出器ではミューオンの飛跡検出をそれぞれ行っている。検出器の概観は図 1.2 に示す。

ATLAS 検出器では、座標系として、ビームパイプの衝突点の中心を原点とし、x 軸を LHC の中心方向、y 軸を地上方向、z 軸をビームパイプに沿って取ったものを使用している。また、z 軸周りの角度を $\varphi$ 、z 軸となす天頂角を $\theta$ としている。 $\theta$  に関しては、擬ラピディティ $\eta$ と呼ばれる座標を用いている。 $\eta$  は、 $\eta=-\ln\tan\frac{\theta}{2}$  で定義される。これは、粒子同士の衝突によって生成される粒子の多くが、z 軸に沿って生成されることから用いられている。

図 1.2 ATLAS 検出器の概観図 [2]

#### 1.2.1 内部飛跡検出器

ことが予定されている。

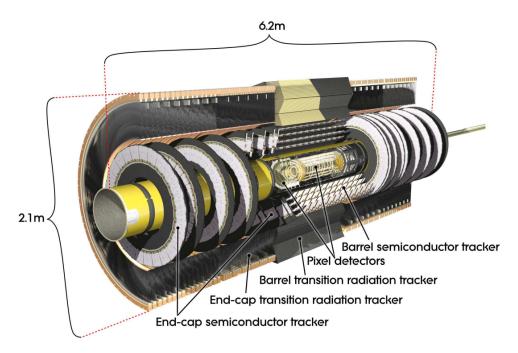

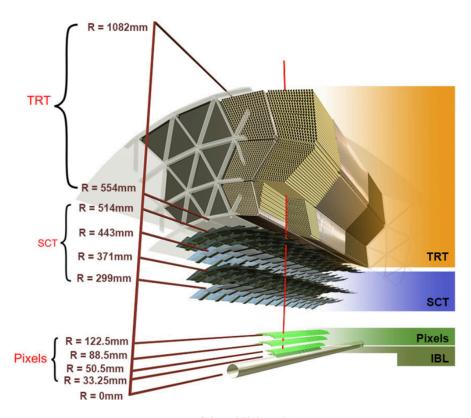

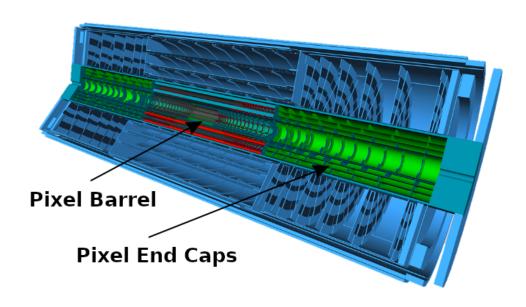

内部飛跡検出器は、ATLAS 検出器の最内層に設置されている検出器である。内側から、IBL、pixel 検出器、SCT 検出器、TRT 検出器で構成されている。各検出器によって、荷電粒子の運動量や電荷の測定を行っている。内部飛跡検出器内部には、ソレノイド磁石によって 2 T の一様な磁場がかけられているため、ローレンツ力による荷電粒子の飛跡変化における曲率から運動量を求めている。内部飛跡検出器の概観図を図 1.3 に示す。また、内部飛跡検出器の断面図を、図 1.4 に示す。検出器には、バレル部とエンドキャップ部が存在し、それぞれバレル部はビームパイプを円筒状に覆うように、エンドキャップ部はディスク上でビームパイプに直交するように配置されている。この内部飛跡検出器全体で、 $|\eta|$  < 2.5 の領域で荷電粒子の計測を行っている。HL-LHC 実験のアップグレードに際して、内部飛跡検出器は、ITk と呼ばれる半導体検出器に置換される

#### ・IBL、pixel 検出器

IBL(Insertable B-layer) と pixel 検出器は、内部飛跡検出器の最内層を構成するシリコン半導体ピクセル検出器であり、荷電粒子の飛跡を二次元で読み出している。IBL は、ビームパイプから 33 mm に位置している、Run2 から ATLAS 検出器に追加された検出器である。pixel 検出器は、バレル部とエンドキャップ部がそれぞれ 3 層ずつ存在し、内側に IBL が追加されているため、4 層のシリコンピクセル検出器で構成される。バレル部の pixel 検出器は、ビームパイプからそれぞれ 50.5 mm、88.5 mm、122.5 mm の位置に配置されている。ピクセルサイズは、IBL の層は  $50 \times 250 \, \mu \text{m}^2$ 、pixel 検出器の層は  $50 \times 400 \, \mu \text{m}^2$  となっている。位置分解能は、動径方向、方位角方向で  $10 \, \mu \text{m}$ 、z 軸方向に  $115 \, \mu \text{m}$  である。

#### ・SCT 検出器

SCT(SemiConductor Tracker) 検出器は、pixel 検出器の外層に設置されたシリコン半導体ストリップ型 検出器である。バレル部が 4 層、エンドキャップ部が 9 層で構成されている。SCT 検出器のバレル部は  $|\eta|<1.4$  の領域をカバーしている。SCT 検出器のモジュールは、2 つのセンサーで構成されており、センサーを 40 mrad の角度を付けて重ねることで、二次元読み出しを実現している。位置分解能は、動径方向、方位 角方向で 17  $\mu$ m、z 軸方向に 580  $\mu$ m である。

#### ·TRT 検出器

TRT(Transition Radiation Tracker) 検出器は、混合気体を利用したガス検出器である。混合気体は、70%がキセノン、27%の二酸化炭素、3%の酸素からなる。直径 4 mm の金メッキ済みタングステンを陽極としたドリフトチューブに混合気体を封入したものを、バレル部で 73 層、エンドキャップ部で 160 層を積み重ねることで検出器が構成されている。荷電粒子が異なる物質間を移動すると起こる現象である遷移放射を利用し、荷電粒子が検出器を通過する際に、混合気体の電離によって発生する電子を読み出すことで粒子の計測を行っている。位置分解能は、動径方向、方位角方向で  $130~\mu m$  である。

図 1.3 内部飛跡検出器の概観図 [3]

図 1.4 内部飛跡検出器断面図 [4]

#### 1.2.2 カロリメータ

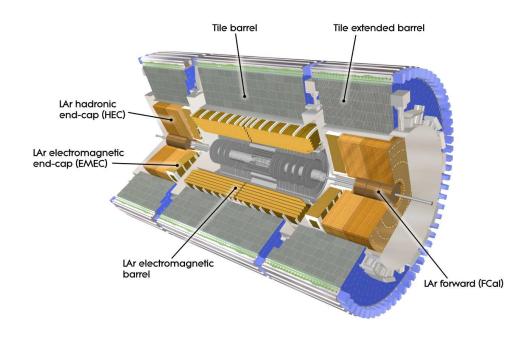

カロリメータは、内部飛跡検出器の外側に配置されている検出器である。カロリメータの概観図を図 1.5 に示す。カロリメータでは、通過した粒子の通過位置やエネルギーの測定が行われている。電磁カロリメータとハドロンカロリメータの 2 種存在し、検出器の内側から電磁カロリメータ、ハドロンカロリメータで構成される。それぞれ、電子や光子のエネルギー測定、ハドロンのエネルギー測定を行っている。これらの粒子のエネルギー測定を行うために、吸収層は物質量が大きい物質で構成される。

#### ・電磁カロリメータ

電磁カロリメータにおいては、電子や光子のエネルギー測定が行われている。吸収層は鉛、検出層は液体アルゴンが用いられている。吸収層の鉛によって電子や光子が電磁シャワーを起こして静止することを利用し、検出層のアルゴンシンチレータで電子や光子のエネルギーを測定している。電磁カロリメータは、バレル部に1つ、エンドキャップ部に2つ設置されており、 $|\eta|$  < 3.2 の領域をカバーしている。

#### ・ハドロンカロリメータ

ハドロンカロリメータにおいては、ハドロンと原子核の強い相互作用によって発生するハドロンシャワーを利用してハドロンのエネルギー測定が行われている。バレル部とエンドキャップ部で構成要素が異なる。バレル部では吸収層に鉄、検出層にプラスチックシンチレータが用いられており、エンドキャップ部では、吸収層に銅、検出層に液体アルゴンシンチレータが用いられている。この検出器は、 $|\eta|<4.9$ の領域をカバーしている。

図 1.5 カロリメータの概観図 [5]

1.3 トリガーシステム 1 *LHC-ATLAS* 実験

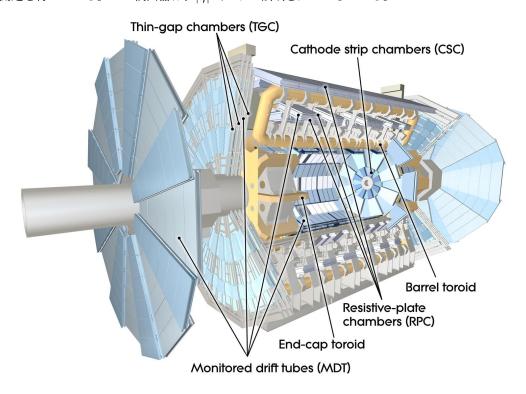

#### 1.2.3 ミューオン検出器

ミューオン検出器は、ATLAS 検出器の最外層に設置されている検出器である。ミューオン検出器の概観図を図 1.6 に示す。この検出器は、ミューオンの運動量測定や飛跡再構成を行っている。ミューオン検出器は、4 種類のガス検出器 (RPC、TGC、MDT、CSC) とトロイド磁石で構成される。トロイド磁石によって、カロリメータを通過したミューオンに磁場を加えて粒子の軌跡を変化させ、その曲率からミューオンの運動量や飛跡の測定を行っている。この検出器は、 $|\eta|$  < 2.7 の領域をカバーしている。

図 1.6 ミューオン検出器の概観図 [6]

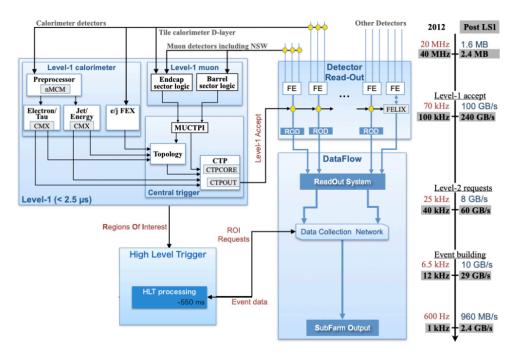

#### 1.3 トリガーシステム

LHC-ATLAS 実験では、陽子同士の衝突は  $40~\mathrm{MHz}$  の頻度で発生しており、この衝突によって生成された 粒子に関するデータの収集が行われている。しかし、実際に収集できるデータ量は、技術的な課題により  $1~\mathrm{MHz}$  程度となっている。そのため、実験で得られた情報の中から重要なもの以外を取り除き、解析の対象と するデータの選別が不可欠である。LHC-ATLAS 実験では、ハードウェアベースで高速の  $1.7~\mathrm{C}$  LT Trigger とソフトウェアベースで高精度の HLT の  $1.7~\mathrm{C}$  段階のトリガーによって情報の取捨選択を行っている。トリガーシステムの概要を図  $1.7~\mathrm{C}$  に示す。

### • L1 Trigger(Level-1 Trigger)

L1 Trigger は、ATLAS 検出器で計測した 40 MHz のイベントレートを 100 kHz まで減少させる。このトリガーは、高速で事象選別を行う必要があるため、論理回路を含むハードウェアによって実装されている。L1

Trigger は、カロリメータとミューオン検出器の情報のみを利用して事象の識別を行っており、カロリメータでの高エネルギー事象やミューオン検出器での高横運動量のミューオン飛跡などを計測した事象を取り出している。この識別において除去されなかった事象は、トリガーとなった要素の位置情報である RoI(Region of Interest) とともに HLT に渡される。

#### • HLT(High-Level Trigger)

HLT は、L1 Trigger によって選別された事象をカロリメータとミューオン検出器の情報に加え、内部飛跡検出器の情報も用いてソフトウェアベースの選別を行う。L1 Trigger からの情報と、L1 Trigger において RoI とされた領域の飛跡を再構成することで、オフラインの解析に近い事象の識別を行う。最終的に識別されたイベントは1kHz 程度まで落とされ、ストレージに保存される

図 1.7 トリガーシステムの概要図 [7]

# 2 HL-LHC 実験

現在、LHC-ATLAS 実験では、2020 年代後半にかけて HL-LHC(High Luminosity-LHC) 実験へのアップグレードが計画されている。この改良は、LHC において、さらに多くのデータ統計を取ることを目的としており、瞬間、積分ルミノシティや粒子衝突頻度の増強が予定されている。LHC のデータ量増加により、ヒッグス粒子の未知の性質の解明や標準模型を超えた新物理探究への貢献を目指している。このアップグレードに伴う現行の LHC 実験と HL-LHC 実験のパラメータの違いを表 2.1 に示す。

| パラメータ    | LHC                                                    | HL-LHC                                                 |

|----------|--------------------------------------------------------|--------------------------------------------------------|

| 重心系エネルギー | 13.6 TeV                                               | 14 TeV                                                 |

| 瞬間ルミノシティ | $2.0 \times 10^{34}  \mathrm{cm}^{-2} \mathrm{s}^{-1}$ | $7.5 \times 10^{34}  \mathrm{cm}^{-2} \mathrm{s}^{-1}$ |

| 積分ルミノシティ | $300 \; {\rm fb^{-1}}$                                 | $3000 \; {\rm fb^{-1}}$                                |

表 2.1 LHC と HL-LHC のパラメータ比較

# 2.1 検出器のアップグレード

表 2.1 から分かるように、アップグレード後は積分ルミノシティが 10 倍ほどになることが期待されている。LHC の HL-LHC へのアップグレードにより、瞬間ルミノシティもバンチの衝突頻度も数倍ほど増加し、統計量が増えることから、検出器の放射線損傷や検出粒子数増加に伴う読み出しの増加への対策が必要となる。特に、放射線損傷に関しては、現行の内部飛跡検出器では想定されるダメージに耐えられないと予想されている。そのため、ATLAS 検出器においては、現行の内部飛跡検出器を  $ITk(Inner\ Tracker)$  と呼ばれるシリコン半導体検出器に置換する計画が進んでいる。ITk 実装後の飛跡検出器の予想図を図 2.1 に示す。また、HL-LHC 実験の計画を図 2.2 に示す。

図 2.1 ITk 検出器予想図 [8]

図 2.2 HL-LHC 計画 [9]

# 3 ITk(Inner Tracker)

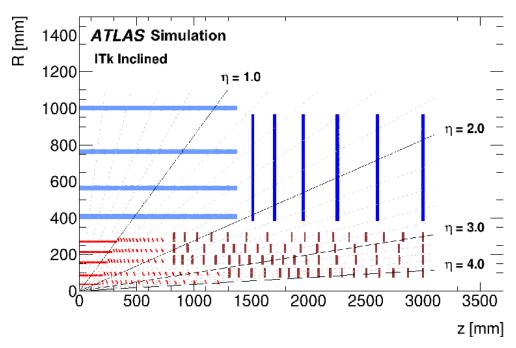

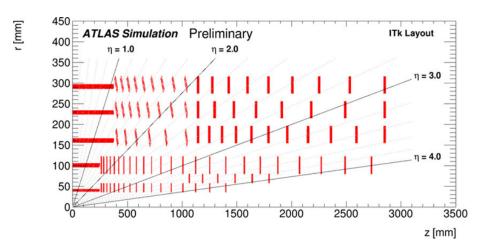

ITk 検出器は、シリコンセンサーを用いた半導体検出器である。HL-LHC 実験において、ATLAS 検出器最内層の内部飛跡検出器の代わりに実装されることが予定されている。ITk 実装後の検出器のビームパイプ方向の断面図を図 3.1 に示す。ここで、原点はビームの衝突点、横軸はビームパイプと平行な z 軸方向、縦軸は原点からの半径を表している。ITk 検出器は、シリコンピクセル検出器とシリコンストリップ検出器の 2 種の検出器で構成されている。図 3.1 において、内側の赤い部分がシリコンピクセル検出器を、外側の青い部分がシリコンストリップ検出器を表す。シリコンピクセル検出器は、ピクセル状のシリコンセンサーを用いて二次元の位置情報を得る検出器であり、バレル部とエンドキャップ部がそれぞれ 5 層ずつで構成される。シリコンピクセル検出器部では、 $|\eta| < 4$  の領域をカバーしている。また、シリコンストリップ検出器は、一次元で読み出すセンサーを角度を付けて重ねることで二次元の読み出しを可能とする検出器である。こちらはバレル部が 4 層、エンドキャップ部が 6 層で構成されており、 $|\eta| < 2.7$  の領域をカバーしている。本論文では、主にシリコンピクセル検出器について述べる。ピクセルモジュールの性能を表 3.2 に示す。シリコンピクセル検出器は、フレキシブル基板、シリコンピクセルセンサー、FE チップから構成される。それぞれの詳細については後述する。

図 3.1 ITk 検出器ビームライン方向断面図 [10]

| パラメータ   | 数値                        |

|---------|---------------------------|

| チップサイズ  | $20.0 \times 20.0 \ mm^2$ |

| ピクセル数   | $400 \times 384$          |

| ピクセルサイズ | $50 \times 50 \ \mu m^2$  |

| 転送レート   | $5120~\mathrm{Mbit/s}$    |

| 放射線耐性   | 500 Mrad                  |

表 3.1 ITk ピクセルモジュールの性能

### 3.1 半導体検出器

シリコンピクセル検出器に関して述べるに際し、まず、半導体検出器について述べる。

## 3.1.1 半導体

半導体とは、金属をはじめとする導体とゴムなどの絶縁体の中間の性質を持つ物質のことである。代表的な例として、前述のシリコンやゲルマニウムなどが挙げられる。物質には、電子が自由に移動することのできる伝導帯と電子が束縛されている価電子帯が存在し、その間には電子が存在することのできないバンドギャップと呼ばれる領域が存在する。導体はこのバンドギャップがほぼ存在しない物質のことを、絶縁体は大きなバンドギャップを持つ物質のことを指している。半導体は、バンドギャップは存在するものの、伝導帯から価電子帯への遷移に必要なバンドギャップエネルギーが、数 eV 程度であるという性質を持っている。そのため、熱などのエネルギーを与えることで、価電子帯の電子の一部が伝導帯へと遷移し、電気伝導が発生する。

#### 3.1.2 半導体の種類

半導体には、大別すると真性半導体、n型半導体、p型半導体の3種類が存在する。

#### · 真性半導体

真性半導体は、不純物を加えていない純粋な半導体である。この半導体の性質は絶縁体に近く、電圧をかけてもほとんど電流は流れない。

一方、n 型半導体と p 型半導体は、不純物を加える (ドープする) ことで電荷を運ぶキャリアの密度を高め、 導体のような性質を得た半導体である。

#### ・n 型半導体

原子価が 4 であるシリコンに不純物を加える場合、原子価が 5 であるヒ素やリンをドープすると n 型半導体となる。この際に添加した不純物は「ドナー」と呼ばれる。5 価の元素は、シリコンとの共有結合において電子を一つ余らせるが、この余剰電子は結晶内のクーロン力によって弱く束縛されているだけであることから、比較的少ないエネルギーで自由電子として振る舞うことができる。結果として、n 型半導体では電子がキャリアとして電気伝導を担っている。

#### ・p 型半導体

他方、p 型半導体は、シリコンに原子価が 3 であるホウ素やアルミニウムをドープした半導体である。p 型 半導体に添加した不純物は「アクセプタ」と呼ばれる。3 つの価電子を持つ元素は、シリコンとの共有結合において電子が一つ足りないため、この不足している部分に正孔と呼ばれる領域が生じる。正孔には、常に周囲の価電子が入り込もうとする。この正孔周辺の電子が移動する過程が繰り返されることで、正孔は正の電荷を持った電子のように振る舞い、電流を運ぶこととなる。結果として、p 型半導体の内部では正孔が電気伝導のキャリアとして働く。

#### 3.1.3 pn 接合による荷電粒子の検出

n 型半導体と p 型半導体の接触面のことを、pn 接合と呼ぶ。異なる種類の半導体が接触することにより、 n 型半導体の電子が p 型半導体側へ、p 型半導体側の正孔が n 型半導体側へ拡散する。この際に、それぞれのキャリアは接合部付近で結合、消滅するため、接合部に空乏層と呼ばれるキャリアの乏しい領域が形成される。この空乏層の形成に伴い、空乏層内に電荷の偏りが生まれるため、内部電場が発生する。この電場は、キャリアのさらなる拡散を抑制する方向に働くことから、pn 接合は整流作用を特性として示す。具体的には、pn 接合に順方向バイアスをかけると、内部電場が弱まるため、電子と正孔が移動しやすくなり、結果として電流が流れやすくなる。一方で、逆バイアスをかけた場合には、内部電場が強まることから、電流がほとんど流れなくなるという性質である。

また、pn 接合を用いた荷電粒子の検出についても述べる。pn 接合を利用した半導体検出器は、放射線や荷電粒子の計測に幅広く用いられている。この検出器は、pn 接合で形成される空乏層とその内部電場を活用したものである。具体的な動作原理について説明する。外部から半導体の空乏層内に荷電粒子が入射すると、粒子が半導体を構成する物質と相互作用を起こす。この相互作用によって、荷電粒子から物質にエネルギーが与えられ、空乏層内に電子と正孔が生成される。この電子正孔対の生成数は、粒子のエネルギーに依存してお

り、荷電粒子が空乏層を通過した際に、ベーテ・ブロッホの式に従って粒子が失ったエネルギー量に比例して決定される。空乏層の内部電場は、生成された電子をn型半導体側に、正孔をp型半導体側に引き寄せるため、これらのキャリアによって運ばれた電荷を外部回路によって計測することができる。前述の通り、生成されるキャリア数は荷電粒子のエネルギーに依存しているため、半導体による粒子の検出は、定量的に荷電粒子のエネルギーを測定可能であることが利点となっている。また、pn接合を利用した半導体検出器は、空乏層の厚さを制御することで感度を調整することもできる。例えば、半導体に逆バイアスを加えると空乏層が拡大するため、より多くの電子正孔対を収集できるようになる。これにより、検出器のエネルギー分解能や検出効率を向上させることが可能な点も長所として挙げられる。

#### 3.1.4 放射線損傷

次に、半導体検出器の放射線損傷について述べる。半導体検出器の放射線損傷は、主に非電離損傷と電離損傷の2種類が存在する。ここでは主に、半導体検出器のバルク材料に対して影響を与える非電離損傷について述べる。

非電離損傷は、入射粒子によって半導体を構成するシリコンなどの物質の結晶格子が物理的に破壊されることによって生じる。高エネルギーの粒子が半導体中の原子と弾性的に衝突すると、入射した粒子が結晶格子内の原子にエネルギーを伝達するため、原子が格子中からはじき出される。これにより、半導体内に格子間原子や空孔が形成され、格子欠陥が生じる。さらに、入射粒子のエネルギーが十分に大きい場合、入射粒子との弾性衝突により弾かれた粒子が、結晶中を移動する際に他の原子とさらに衝突するといった格子変位の連鎖が発生することもある。こういったクラスター欠陥は、電子や正孔を捕獲してキャリアの移動を阻害するなどして、検出器の動作に影響を及ぼしている。非電離損傷による影響の例として、型変換や漏れ電流の増加、信号電流の減少などが挙げられる。

# 3.2 シリコンピクセルセンサー

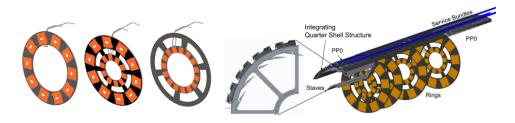

シリコンピクセル検出器は、図 3.2、3.3、3.4 に示されるインナーシステム、エンドキャップ、アウターバレルによって構成される。

図 3.2 インナーシステム [11]

図 3.3 エンドキャップ [11]

図 3.4 アウターバレル [11]

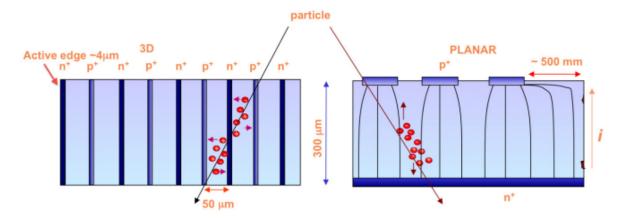

ITk には、プラナーセンサーと 3D センサーの 2 種類のセンサーが用いられる。プラナーセンサーは、センサー面と電極が平行に並んでいるセンサーを指す。 3D センサーは、電極がセンサー面に対して垂直に配置されているため、電極間が狭く、低い電圧で稼働できるという利点がある。加えて、電子正孔対が電極に到達しやすく、格子欠損によるホールに電子が捕らえられにくいという特徴も持っている。そのため、3D センサーは高放射線耐性センサーであり、放射線損傷の影響が大きい検出器最内層に搭載される。それぞれのイメージ図を図 3.5 に示す。

図 3.5 (左)3D センサーのイメージ図 (右) プラナーセンサーのイメージ図 [12]

現行のピクセル検出器においては、これらのセンサーに  $n^+-in-n$  型のシリコンセンサーが用いられている。  $n^+-in-n$  型シリコンセンサーは、n 型半導体に  $n^+$  の電極を埋め込んだ半導体センサーであり、 $n^+$  は 半導体に導入した不純物の量が多いことを、in は絶縁体 (insulator) を指している。このセンサーは、放射線によって損傷すると、型変換によってセンサーの読み出し電極と反対側から空乏化が始まるため、電極に電荷を収集するためには全空乏化させて運用する必要があるが、全空乏化電圧が大きくなるにつれ、このような方法での運用が厳しくなるという問題点が存在する。HL-LHC 実験では、瞬間ルミノシティなどの上昇により、高放射線環境が想定されるため、プラナーセンサー、3D センサーともに放射線耐性の高い  $n^+-in-p$  型シリコンセンサーが用いられる。 $n^+-in-p$  型センサーの放射線耐性が高い理由としては、空乏化が電極側から始まるため、全空乏化電圧が上がっても、部分空乏化で信号読み出し可能であることが挙げられる。他にも、 $n^+-in-n$  型センサーはシリコンの両面にプロセスを施す必要があるのに対し、 $n^+-in-p$  型センサーは片面のみのプロセスで済むため、コストが低いという利点も存在する。 $n^+-in-p$  型センサーのイメージ図を図 3.6 に示す。

図 3.6  $n^+ - in - p$ 型センサーのイメージ図

# 3.3 FE チップ (Front-End IC chip)

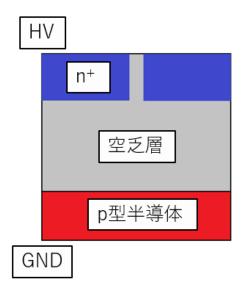

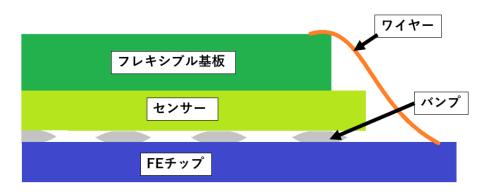

FE チップは、シリコンセンサーに荷電粒子が入射した際の信号を後述するフレキシブル基板に転送している。荷電粒子が検出器に入射した場合、そのエネルギー損失に応じて電子正孔対が生成される。ここで、電子が電極で収集されることで、アナログ信号が FE チップに入力されることとなる。FE チップは、この信号を整形、増幅した後にデジタル信号へと変換し、ボンディングされたワイヤーを通してフレキシブル基板へと転送する。図 3.7 に ITk モジュールの FE チップの動作のイメージ図を示す。バンプとは、Sn-Ag 製で直径 10~20  $\mu m$  の球体であり、センサーと FE チップそれぞれの各ピクセル間を電気的に接続している。ピクセル検出器の場合、バンプはピクセルと一対一対応で並べられるため、ピクセル数と同数のバンプが存在する。

図 3.7 ITk ピクセルモジュールの FE チップの動作のイメージ図

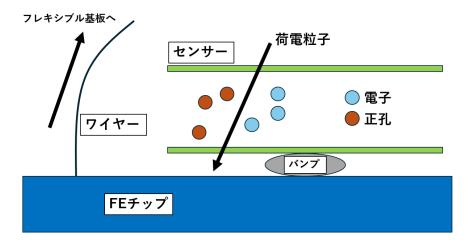

#### 3.4 フレキシブル基板

フレキシブル基板は、柔軟性を持ち、繰り返し変形させることのできる基板に表面実装を行って電気回路を形成した基板のことであり、ITk モジュールにおいては FE チップから送られてきたデジタル信号をデータベースに転送する役割を担っている。FE チップとフレキシブル基板は、約 600 本のアルミワイヤーで電気的に接続されている。加えて、モジュールへの電源供給や温度確認といったモジュールの状態の管理もフレキシブル基板の役割である。フレキシブル基板のサイズは、 $40.39 \times 40.39 \ mm^2$  であり、厚さは  $200 \ \mu m$  である。

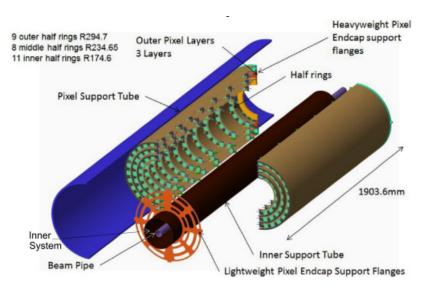

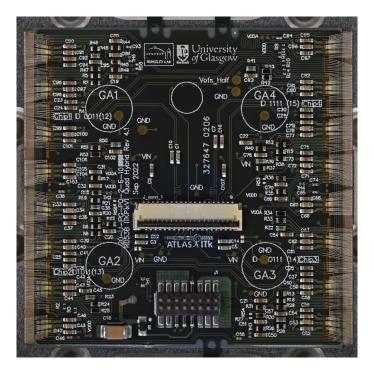

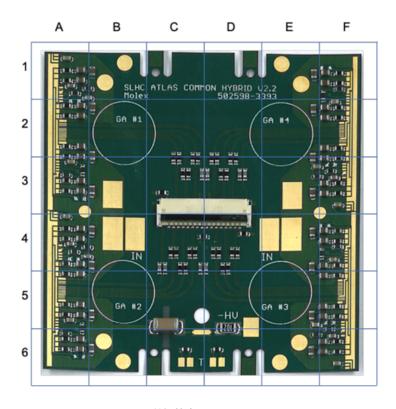

#### 3.5 ピクセル Quad モジュール

ITk モジュールは取り付けられる FE チップの数によって種類が異なり、それに伴って品質試験の内容も異なっている。FE チップが 4 枚、センサーが 1 枚で構成されるモジュールは Quad モジュール、FE チップとセンサーが共に 3 枚ずつで構成されるモジュールは Triplet モジュールと呼ばれる。それぞれのモジュールの外観図を図 3.8、図 3.9 に示す。Quad モジュールと Triplet モジュールを実装した際の検出器のビームパイプ方向の断面図を図 3.10 に示す。外側に Quad モジュール、内側に Triplet モジュールが実装される。前述したように ITk には、プラナーセンサーと 3D センサーが用いられる。それぞれの層で用いられるセンサーやモ

ジュールについては、表 3.2 に示す。また、モジュールの構成の概要図を図 3.11 に示す。つまり、図 3.8 で見られるモジュールのほとんどは、フレキシブル基板である。ここで、ベアモジュールとは、シリコンセンサーと FE チップをバンプで接続したものである。

図 3.8 ITk ピクセル Quad モジュール [11]

図 3.9 ITk ピクセル Triplet モジュール [13]

図 3.10 ITk モジュール実装後の検出器断面図 [14]

表 3.2 ITK 各層で用いられるセンサーやモジュールの詳細

| 層       | センサー                | ピクセルサイズ                            | モジュール   |

|---------|---------------------|------------------------------------|---------|

| L0 バレル部 | $3D n^+ - in - p$   | $25 \times 100 \ \mu \mathrm{m}^2$ | Triplet |

| L0 リング部 | $3D n^+ - in - p$   | $50 \times 100 \ \mu \mathrm{m}^2$ | Triplet |

| L1      | プラナー $n^+ - in - p$ | $50 \times 50 \ \mu\mathrm{m}^2$   | Quad    |

| L2~4    | プラナー $n^+ - in - p$ | $50 \times 50 \ \mu\mathrm{m}^2$   | Quad    |

図 3.11 ITk モジュールの構成イメージ図

# 4 プロダクション

2020 年代後半に計画されている LHC-ATLAS 実験の HL-LHC 実験へのアップグレードに向け、世界各国 の機関で ITk モジュールの生産が進んでいる。ピクセルモジュールは、全世界で約 10000 個の量産が予定されており、日本グループでは、そのうち約 3000 個の量産を行う予定である。このモジュールの量産にあたって、モジュールの組み立てと品質管理試験が行われている。品質管理試験は、 $QC(Quality\ Control)$  試験とも呼ばれる。モジュールの組み立てと品質管理試験は、いくつかのステージに分かれて行われており、それぞ

れにおいて複数の項目を試験する。そのため、モジュールの完成までに得られる試験結果は非常に多くなる。 よって、結果を特定のデータベースにまとめて、世界各地で行われる試験結果を正確に登録し、後に比較、参 照しやすくする必要がある。品質試験の詳細については後述する。

#### 4.1 日本におけるプロダクション

ここでは、日本における ITk 量産について述べる。前述の通り、日本では約 3000 個のピクセルモジュールが生産される予定である。この量産工程は、ベアモジュールとフレキシブル基板の接着から開始される。日本の量産体制として、センサーと FE チップの製造が浜松ホトニクス、フレキシブル基板の製造が山下マテリアルで行われている。また、センサーと FE チップを組み合わせたベアモジュールの品質試験が高エネルギー加速器研究機構 (KEK) で行われている。さらに、千葉県館山市にあるハヤシレピック (株) 第 3 事業部において、フレキシブル基板とベアモジュールの組み立てや品質管理試験が行われている。ATLAS 日本グループにおける試験結果の保存は LocalDB と呼ばれるデータベースに行われる。このデータベースは東京科学大学が開発を行っている。モジュールの量産は世界中で行われており、品質試験の各過程においても複数の項目が試験されるため、LocalDB はそれらの結果の正確な管理の一助となっている。また、ITk モジュール量産全体の中央データベースはチェコに設置されており、ユニコーン大学が開発を行っている。ITk モジュールの量産における品質試験の結果はすべてここに保存され、管理される。この中央データベースに集積した試験結果の解析を行い、各モジュールについて調査することでモジュールの品質を保つことを目指す。

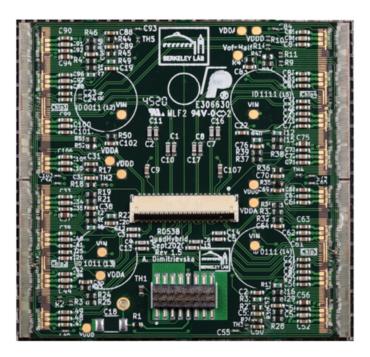

# 4.2 ハヤシレピックの生産体制

これまでハヤシレピックにおいては、ピクセルモジュールの本量産 (Production) を前に、2023 年 6 月から 試験量産 (PreProduction) が進められていた。試験量産では、約 150 台ほどのモジュールについて、初期で は 1 日 1 台、2023 年 11 月以降は 1 日 3 台のペースでモジュールを完成させることを目標として実際に組み立てや品質管理試験が行われており、組み立ての方法の検証や試験結果の確認が行われていた。

また、本量産は 2024 年 10 月ごろに開始された。本量産では、1 日 7 台のペースでのモジュールの完成を目指し、モジュールの量産が進められている。そのため、試験のための設備の増強が行われており、効率的な生産を目指している。具体的な増強の例としては、試験量産では 3 台だったクーリングボックスが、本量産では7 台に増やされていることなどが挙げられる。。本論文では、主にこの試験量産と本量産における品質管理試験の結果解析について述べる。

次に、モジュールの組み立てと品質管理を行っているハヤシレピックにおける生産体制について述べる。ハヤシレピックでは、KEK において品質試験が行われたベアモジュールとフレキシブル基板の組み立てや、組み立てられたモジュールの品質管理試験が行われている。ITk 量産サイトの一つとして LocalDB のサーバーが配備されているため、量産過程で得られる情報をこまめに確認しながら生産を進められる環境となっている。また、外部からの ssh 接続によって、LocalDB や現地の試験設備へアクセスすることができるため、リモートで量産シフトに参画することが可能になっている。このようにサイト外での作業を可能にすることにより、現地シフターとリモートシフターでの分業を行い、高効率なモジュール量産を目指している。

ハヤシレピックの量産サイトの様子を図 4.1 に示す。ここはクリーンルームとなっており、モジュールの品質管理試験や管理が主に行われている。サイト内の設備については以下で述べる。

図 4.1 ハヤシレピックの量産サイトの様子

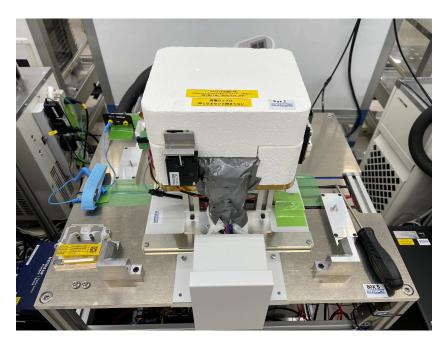

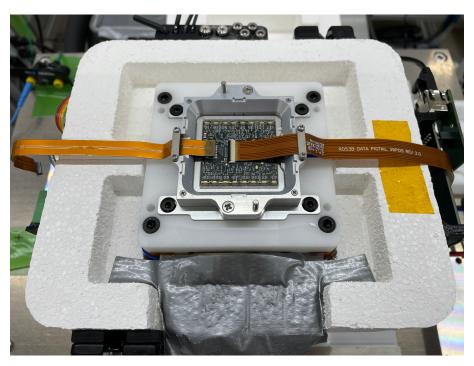

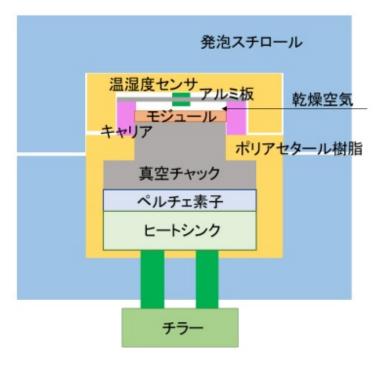

#### ・クーリングボックス

まず、図 4.2 に示すクーリングボックスの説明を述べる。クーリングボックスは、チラーとペルチェ素子で 温度管理された品質管理試験において電気回路読み出し試験を行うための設備となっており、現在7台設置さ れている。主に、断熱性の高いスタイロフォームと呼ばれる素材で構成されている。読み出し試験は、20℃ と-15 ℃の 2 つの状態で行われるため、試験中に設定した温度を保つために保温性の高いスタイロフォームを 使った装置が使われている。また、モジュールを入れた状態で常温からそのまま温度を下げた場合、装置の 内部が結露することでモジュールに水滴が付着し、モジュールの故障の原因となる可能性がある。そのため、 クーリングボックス内は乾燥窒素で満たされており、低露点の状態で保たれている。読み出し試験中はイン ターロックがかけられ、想定外の要因で蓋が開かないように固定される。インターロックは露点によって管理 されており、外部の気温が装置内部の露点より 10 ℃以上高い場合でないと、装置の開放が不可能となってい る。装置の開放や試験環境の設定、モジュールへの電圧印加は、現地コンピュータへの ssh 接続によるリモー ト操作で行うことができるため、現在はリモートシフターがサイト外から読み出し試験を進め、モジュール の交換等は現地シフターが行うという体制で量産が進んでいる。クーリングボックスの内部を図 4.3 で示す。 クーリングボックスの内部は、主にポリアセタール樹脂と呼ばれる素材で構成されており、温度変化の管理が ペルチェ素子で行われている。クーリングボックス内部の構成を図 4.4 に示す。モジュールに被せる部品に は、SHT85という温湿度センサーが取り付けられているため、モジュールが置かれている環境を直接測定可 能となっている。クーリングボックス内の温湿度やモジュールに印加されている電圧などの試験環境に関する 情報は、InfluxDB と呼ばれるデータベースに保存され、Grafana と呼ばれるサービスによってモニタリング している。実際に使用している Grafana の表示を図 4.5 に示す。Grafana とは、様々なデータベースから得 られたデータをリアルタイムで可視化し、Web 上で一度にまとめて表示することができるオープンソースの ダッシュボードツールであり、これによって試験中のモジュールの状態の確認を行っている。Grafana 上には

7台それぞれについて個別に見ることができることに加え、全てのクーリングボックスの状態を同時に確認することも可能である。

図 4.2 クーリングボックスの外観図

図 4.3 クーリングボックス内部の様子

図 4.4 クーリングボックス内部の構成 [15]

図 4.5 Grafana の表示

#### · X 線装置

次に、X 線装置について述べる。X 線装置の外観図を図 4.6 に示す。この装置は、電気回路読み出し試験における試験の一つである、Xrayscan を行うための装置である。Xrayscan は、X 線を使ってモジュールのバンプ剥がれを確認するための試験である。これは、モジュールに 50kV、80uA の X 線を一定時間照射して、

X 線をセンサーに入射させて各ピクセルでのヒット数を確認することで、バンプの状態を調べるという試験となっている。装置自体は、図 4.2 で示されるクーリングボックスの上に被せる形で用いる。安全のため、X 線の照射は Xrayscan を実行するときのみ行われている。

図 4.6 X 線装置の外観図

## 恒温槽

恒温槽についても述べる。恒温槽の外観図を図 4.7 に示す。恒温槽は、品質管理試験の一つである熱サイクル試験に用いられる装置である。ITk モジュールは、HL-LHC 実験で実際に運用されるにあたり、-55 °C  $\sim60$  °Cの範囲での温度変化が起こりうる過酷な環境に実装されるため、温度変化によるモジュールへのダメージを計測するために熱サイクル試験が行われる。熱サイクル試験では、-45 °C  $\sim40$  °Cのサイクルが 10 回、-55 °C  $\sim60$  °Cのサイクルが 1 回行われる。試験後にモジュールの構成要素の熱膨張率の違いによるバンプ剥がれが無いか確認を行い、実際の実験で想定される環境でも問題なくモジュールが動作するかを調べる試験となっている。

図 4.7 恒温槽の外観図

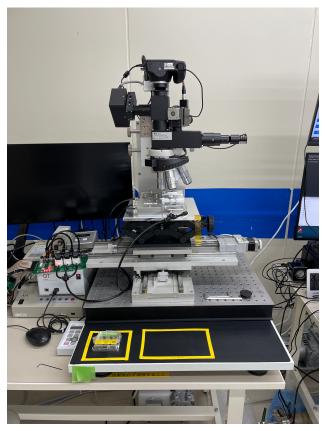

### · 外観測定用顕微鏡

外観測定用顕微鏡を図 4.8 に示す。これは、外観測定に必要な写真撮影を行うための設備となっている。外観測定は、顕微鏡によってモジュールの外観を撮影し、モジュール上の傷や腐食、ワイヤーの断線などを目視で確認する試験である。モジュールを顕微鏡にセットして撮影を開始すると、自動でモジュール全体の撮影を行い、写真がデータベースに保存される。真空引きによってモジュールを固定しているため、撮影途中でモジュールがずれることなく最後まで撮影が行われる。モジュールの裏側を撮影する場合には、一度真空引きを解除して手動でモジュールを裏返す過程が必要となるが、その後は自動で撮影が行われる。顕微鏡やカメラの操作については GUI が整備されているため、簡単に撮影を行うことが可能になっている。

図 4.8 外観測定用顕微鏡の外観図

# ・デシケータ

デシケータの外観図を図 4.9 に示す。デシケータは、試験の順番待ちとなっているモジュールの保管庫としての役割を担っている。モジュール表面に水滴が付着するなどして、故障する可能性を減らすためには低湿度の環境が望ましいため、デシケータの内部は乾燥窒素により温度や湿度が一定に保たれている。そのため、デシケータの扉はできる限り閉まっていることが要求される。デシケータの扉の開閉状況は前述の Grafana でリアルタイムに監視されており、20 分以上連続で扉が開いている場合には、スタッフに警告が入る仕組みが整備されている。

図 4.9 デシケータの外観図

# 5 ITk モジュールの量産

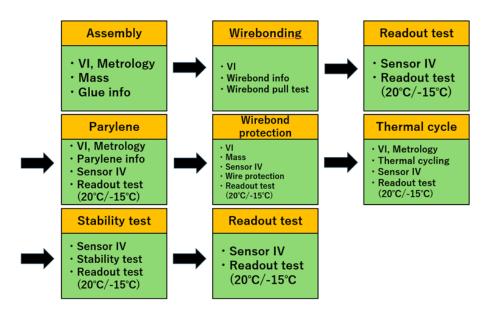

前述した通り、ITk ピクセルモジュールは全世界で約 10000 個量産される予定であり、その内の約 3000 個の Quad モジュールを日本グループが担当することが計画されている。この量産過程において、いくつかのステージに分かれてモジュールの組み立てや品質管理試験が行われる。モジュール量産のステージの流れを図 5.1 に示す。品質管理試験は、各ステージにおいて行われており、それぞれの詳細については後述する。

図 5.1 モジュールの組み立てや品質管理試験の流れ

# 5.1 モジュールのアセンブリ

ITk モジュールのアセンブリは、ベアモジュールとフレキシブル基板を接着するという形で行われる。フレキシブル基板は、ベアモジュールのセンサー側に取り付けられるため、モジュールは上からフレキシブル基板、シリコンセンサー、FE チップという順番で構成される。モジュールの組み立ては、専用の治具を使用して行われる。治具を図 5.2 に示す。モジュールは、まずアライメントピンによって治具に固定される。その後、さらに真空吸着によって固定され、アライメントピンは取り外される。真空吸着後に、フレキシブル基板に Araldite2011 と呼ばれるエポキシ系接着剤が塗布され、部品の接着が行われる。Araldite2011 の物性値を表 5.1 に示す。Araldite2011 は十分な接着強度と放射線耐性を持つことから、モジュールの組み立てに使われる。接着材の塗布する方法としては、ステンシル法が採用される。ステンシル法とは、特定のパターンで穴が開いたマスクを基板の上にかぶせ、マスクの上からヘラで接着剤をすり切ることで、穴の形状に合わせて接着剤を塗布する方法である。接着剤の塗布は手動で行われるため、組み立てを行った人間によって塗布の仕方にばらつきが出にくいステンシル法が用いられている。

図 5.2 (左) ベアモジュール用治具 (右) フレキシブル基板用治具 [16]

表 5.1 Araldite2011 の物性値

| パラメータ  | 物性値           |

|--------|---------------|

| 密度     | $1.05~g/cm^3$ |

| 粘度     | $45000\ mPas$ |

| 熱膨張率   | 85~ppm/K      |

| 使用可能時間 | 2 分           |

| 硬化時間   | 12 時間         |

|        |               |

# 5.2 ワイヤボンディング

ワイヤボンディングでは、FE チップとフレキシブル基板の電気的な接続が行われる。この接続には直径が 25  $\mu$  m のアルミワイヤーが用いられ、ワイヤーボンダーと呼ばれる装置で行われる。ワイヤーボンダーは、ボンドヘッドと呼ばれる部分をワイヤーとモジュール部品のパッド部分に押し当てた上で、超音波を印加する ことでそれらを合金化して接合を行う。その後、ボンドヘッドがもう片方の部品のパッド部分へ移動し、同様 にワイヤーを接合することで一組のパッド同士が電気的に接続される。ワイヤーボンダーの外観図を図 5.3 に示す。

図 5.3 ワイヤーボンダーの外観図 [16]

#### 5.3 パリレンコーティング

パリレンコーティングでは、真空蒸着によってモジュールに約  $5~\mu$  m のパリレン薄膜を形成する。ITk ピクセルモジュールは電圧を印加して使用するため、ピクセルセンサーから放電が起きる可能性が存在する。そのため、センサー等からの放電や湿気、化学物質などによる腐食を防止するため、パリレンコーティングが行われる。日本パリレン社にモジュールを送り、パリレンの蒸着を行っている。また、モジュールには、コネクタ部分など蒸着を避けるべき部分も存在しているため、図 5.4 で示すようにマスクを取り付けることで、保護した状態でパリレンコーティングが行われている。

図 5.4 パリレンコーティングの様子

# 5.4 ワイヤボンドプロテクション

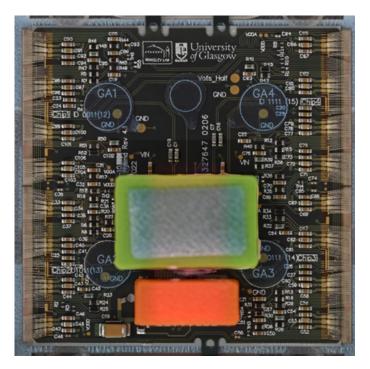

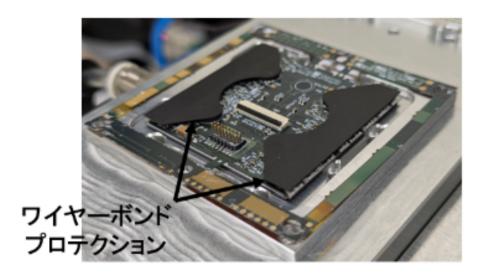

この過程では、ワイヤボンディングによって取り付けられたワイヤーを保護するためのワイヤボンドプロテクションをモジュールに取り付ける。ここでは、モジュールの組み立ての際と同様に専用の治具を使ってプロテクションの取り付けを行う。ワイヤボンドプロテクションは、アウターバレル用のモジュールに取り付けられる。ワイヤボンドプロテクション取り付け後のモジュールの外観図を図 5.5 に示す。

図 5.5 ワイヤボンドプロテクション取り付け後のモジュールの外観図 [17]

## 5.5 耐久試験

耐久試験では、モジュールに電圧を長時間かけ続けた際のモジュールの状態を確認する。この試験では、モジュールの温度を実際に稼働させる場合と同様の-15 °Cに保った状態で、定期的にスキャンを行い、モジュールが HL-LHC 実験で実装された後も安定して動作することを確認するための試験である。

# 5.6 モジュールの品質管理試験

モジュールの品質管理試験は、モジュールのフレキシブル基板や FE チップが正常に動作にするかを確かめるための試験である。この試験を通して不良品を取り除き、各モジュールの動作の均一化を図っている。また、試験でのモジュールごとの特性から、実装される際の取り付け場所を決定することも目的の一つである。それぞれの品質試験には基準値が存在し、この基準値に収まるか否かでモジュールの判別を行っている。図5.1 で示した量産の流れのように、各ステージで行われる品質管理試験が異なっている。ここでは、品質管理試験のうち、いくつかについて述べる。それぞれの品質管理試験について、詳細は以下で述べる。

### 5.6.1 質量測定 (Mass Measurement)

質量測定では、モジュールの質量を 0.1 g の精度で測定する。各工程前後での質量を比較することにより、組み立ての際に使用した接着剤の質量や、ワイヤーの質量等を調べることができる。

#### 5.6.2 外観測定 (Visual Inspection)

質量測定では、前述した外観測定用顕微鏡で図 5.6 で示すようにモジュールの外観を撮影し、モジュール上に傷や汚れ、腐食やワイヤーの断線などを目視で確認する。また、モジュールの組み立ての際に使用した接着剤が漏れ出していないか等も確認する。実際には、図 5.7 のように撮影した画像を分割し、各ブロックごとに目視での確認を行っている。

図 5.6 外観検査に用いられる画像の例

図 5.7 外観検査のイメージ図 [18]

#### 5.6.3 サイズ測定 (Metrology)

この試験では、外観測定と同様に顕微鏡によって撮影した画像を用いて、モジュールの辺の長さや高さ、歪み等を測定する。組み立ての過程において、ずれ等が問題が生じていないかを確認している。

#### 5.6.4 電気回路読み出し試験

電気回路読み出し試験では、実際にセンサーと FE チップに電圧をかけてモジュールの動作を確認し、センサーの不具合の有無や電流-電圧特性等を調べている。また、各ステージでのモジュールの状態を確認し、ワイヤーの断線等の問題がないか確認している。この試験の詳細については後述する。本論文では、主に電気回路読み出し試験の結果解析について述べる。

# 6 ITk モジュールの試験結果解析

### 6.1 電気回路読み出し試験

電気回路読み出し試験は、前述の通り、実際にモジュールに電圧を印加して、動作を確認する試験である。モジュールをクーリングボックスに入れ、温度を維持できる状態で試験が行われる。基本的に、試験は  $20\,^\circ$ C もしくは- $15\,^\circ$ Cで行われ、それぞれ warm テスト、cold テストと呼ばれる。印加される電圧は、基本的に HV が約  $80\,$ V、LV が約  $2.3\,$ V である。HV はセンサーに印加するバイアス電圧であり、LV はモジュールの回路を動作させるための電圧である。読み出し試験には、複数の過程が存在しており、それぞれの詳細については後述する。

### 6.1.1 接続の確認

この過程では、モジュールとの接続を確認し、試験を通してモジュールから結果が得られるか否かを確認する。以下の二つの試験を行う。Cold power-up test については、cold テストでのみ行う。

#### · Cold power-up test

-35 °Cで LV のみ印加し、正しくモジュールと測定のためのコミュニケーションを確立できるかを確認を行う。

## $\boldsymbol{\cdot}$ Chip configuration

FE チップに対して config を渡し、通信を確立できるかどうかを確認する。

### 6.1.2 IV scan

印加する HV を 5 V 刻みで 0 V から 200 V まで変えながら、センサーの漏れ電流を測定する。また、モジュールの電流-電圧特性を調べることで、試験中などにおけるセンサーの故障などを確認する。

#### 6.1.3 simple scan

simple scan は、モジュールの基本的な機能の動作確認を行うための試験である。複数のパラメータについて試験を行うため、以下にそれぞれの詳細を示す。本論文では、主に simple scan の結果解析を行ったため、

その詳細について述べる。

#### · ADC calibration

ADC(アナログ信号をデジタル信号に変換する機器) に電圧を入力して、それに比例してデジタル信号が得られるかを確認する。印加する電圧を 0.1~V から 0.7~V まで変えながら、出力 ADC 値との関係やリニアリティ、オフセットを測定する。ADC calibration の試験結果の例を図 6.1 に示す。

図 6.1 ADC calibration の試験結果の例 [17]

#### Analog readback

アナログ回路やデジタル回路への電源供給の状態を確認する。アナログマルチプレクサで FE チップ内の様々なパラメータに対応する電圧および電流を読み出し、それらの値に問題がないか確認する。Analog readback で行われる測定について、以下で述べる。

電圧測定: モジュールに電流を流し、各部の電圧および電流を測定する。

温度測定: チップの analog SLDO 付近、digital SLDO 付近とリングオシレータ付近に存在する温度センサーの電圧を測定する。

VDDA/D と trim の関係測定: VDDD、VDDA は、それぞれデジタル部とアナログ部の SLDO 出力で、回路を動作させる電源電圧を担う。電源電圧の値を  $1.2~\rm V$  に近づけるため、モジュール上の Iref trim ワイヤー により 4-bit DAC を設定している。また、VrefA、VrefD それぞれに付随した 4-bit DAC によって、Vref を調整することで値を変更できる。この測定では、DAC 値  $({\rm trim})$  を 0 から 15 まで変更したときの VDDD、VDDA の変化を測定する。この測定の結果の例を図  $6.2~\rm k$ に示す。

図 6.2 VDDA/D と trim の関係測定の結果の例 [17]

リングオシレータ測定: チップには、論理回路への放射線損傷を調べるため、様々な論理回路で構成されたリングオシレータが存在する。 VDDD 測定と同様に trim 値を変更することでリングオシレータに対する VDDD の値を変えながら周波数を測定し、リングオシレータの状態を確認する。この測定の結果の例を図 6.3 に示す。

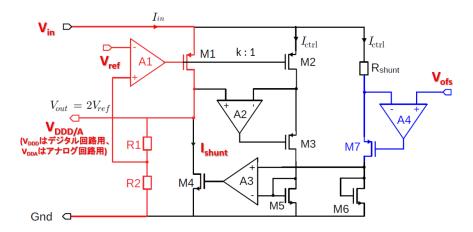

·SLDO

デジタル回路とアナログ回路にそれぞれ電源電圧を供給している SLDO(Shunt Low Drop Out) レギュレータの動作確認を行う。レギュレータに対する入出力電圧電流等を測定し、特に、デジタル部とアナログ部

の電圧や電流の一致を要求している。この測定では、以下の値を測定する。SLDO における測定結果の例を図 6.4 に示す。

SLDO の出力電圧: VDDD/A

SLDO への入力電圧、入力電流: VinD/A、IinD/A

Iin ごとに測定したアナログ部とデジタル部への入力電圧の差の最大値: max(|VinA(Iin) - VinD(Iin)|)

オフセット電圧: Voffset リファレンス電流: Iref シャント電流: IshuntD/A

図 6.4 SLDO の結果の例 [17]

SLDO レギュレータの回路を図 6.5 に示す。SLDO レギュレータにおいては、出力電圧である VDDD/A が回路内の基準電圧となるリファレンス電圧 Vref の 2 倍を保つように調整されている。そのために、トランジスタ (図 6.5 中の A1) に誤差アンプ (図 6.5 中の M1) がフィードバックを与えている。また、コスト削減のため、ITk の実装において、モジュールを動作させるための電源は、 $6\sim12$  モジュールに対して直列に接続 (serial powering) し、その電源電流を並列で各モジュールの 4 つのチップに給電するという手法が取られている。SLDO はこの給電方法をサポートする役割を担っている。つまり、SLDO は、直列に接続されている各モジュールの状態に関わらず、SLDO が供給された電源電流を調整し、チップでの電圧を一定にすることで、モジュールの外部から見た場合に各モジュールでの電圧降下を一定にすることに寄与している。シャント回路 (図 6.5 中の A4 部分) が可変抵抗のように振る舞うことで、このような実効的な電圧降下を一定にするような動作が見られる。さらに、オフセット電圧 Vofs は、入力電流と出力電圧との関係にオフセットを与え、SLDO の出力を図 6.6 で示すようにしている。加えて、SLDO レギュレータは、デジタル回路用とアナログ回路用それぞれ独立に設けられている。これは、デジタル回路において発生したノイズがアナログ回路に影響しないようにするためである。SLDO は、モジュールに安定した動作電源を供給するという重要な役割を担っているため、この部分に不具合があると、モジュールの動作に大きな悪影響があると考えられる。よって、品質管理試験において、特に留意して試験を進める必要がある。

図 6.5 SLDO レギュレータの回路図 [17]

図 6.6 SLDO レギュレータの出力 [17]

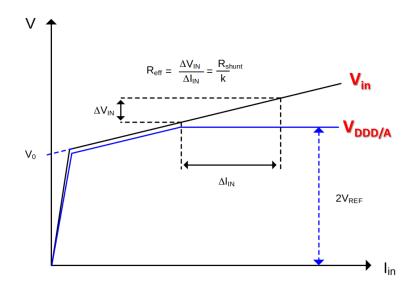

### $\cdot$ Vcal calibration

デジタル信号をアナログ信号に変換する機器のキャリブレーションを行う。テスト電荷を生成するための 2 つの電圧をキャリブレーションする。電圧の値を変えるための DAC を変えながら、その時の電圧値をマルチプレクサから出力し、測定する。 Vcal calibration の試験結果の例を図 6.7 に示す。

図 6.7 Vcal calibration の試験結果の例 [17]

### · Injection capacitance

モジュールの試験用入射電荷の静電容量の確認を行う。試験電荷を生成するための injection capacitance を測定し、その値が 6.74-9.00 fF の範囲に入っていることを確認する。

# · Low power (LP) mode

低印加電圧の状態でモジュールが正常に動作するかを確認する。Low power mode は、モジュールの最低限の機能のみを有効化して低消費電力を実現する状態のことである。これは、検出器量産の過程で、coolingが取り付けられていない場合に、モジュールの状態を確認する際に用いられる。この試験では、以下の値を測定する。

SLDO への入力電圧、入力電流: VinD/A、IinD/A

オフセット電圧: Vofs シャント電流: IshuntD/A

# · Data transmission

データの状態を確認するため、eye diagram の開き具合を測定する。

#### 6.1.4 YARR scan

YARR scan では、様々なスキャンを行い、ピクセル単位での問題の確認や threshold の設定などのキャリブレーションを行なう。YARR(Yet Another Rapid Readout) とは、モジュール用の DAQ(Data Acquisition) システムである。ここでは、MHT、TUN、PFA の三つの試験を行う。それぞれで行われる試験は、以下の通りである。

### • MHT(Minimum health test)

Digital scan

Analog scan

Threshold scan (high range)

ToT scan

## • TUN(Tuning)

Global threshold tune (threshold = 2000 e-)

Threshold scan (high range)

ToT scan

ToT tune

Global threshold tune (threshold = 2000 e-)

Pixel threshold tune (threshold = 2000 e-)

Global threshold re-tune (threshold = 1500 e-)

Pixel threshold re-tune (threshold = 1500 e-)

Threshold scan (high definition)

ToT scan

### • PFA(Pixel failure analysis)

Digital scan

Analog scan

Threshold scan (high definition)

Noise scan

${\rm ToT\ memory\ scan}$

Disconnected bump scan

Merged bump scan

Zero bias scan (HV = 0 V  $\mathcal{CO}$  threshold scan)

Xray scan

それぞれのスキャンについての詳細を以下で述べる。

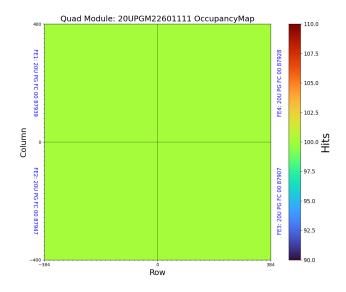

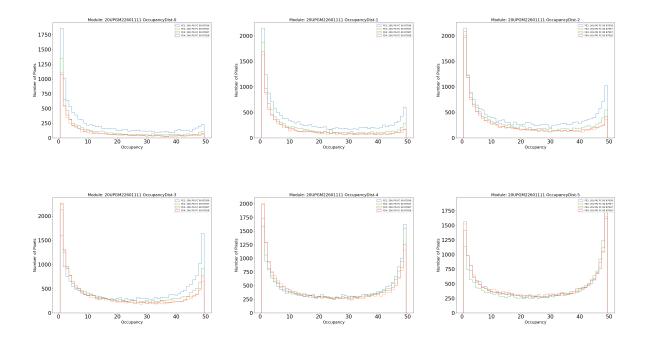

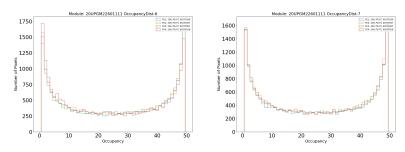

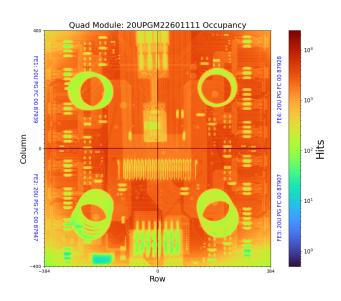

#### · Digital Scan

FE チップのデジタル回路に試験電荷を 100 個入れてその応答を確認する。config の影響を受けにくく、通信の接続や初期の config が成功するかの試験にもよく用いられる。特に、PFA においては、occupancy < 1% の場合は digital dead、occupancy < 98% または occupancy > 102% の場合は digital bad と判定する。正常なモジュールであれば応答率は 100% となり、多くのモジュールですべてのピクセルで 100% の応答が確認される。Digital Scan の試験結果の例を図 6.8 に示す。

図 6.8 Digital Scan の試験結果の例 [17]

#### · Analog Scan

FE チップのアナログ回路に試験電荷を 100 個入れてその応答を確認する。特に、PFA においては、occupancy < 1~% の場合は analog dead、occupancy < 98~% または occupancy > 102~% の場合は analog bad と判定する。正常なモジュールであれば応答率は 100% となる。occupancy が低いピクセルが見られることもあるが、その割合はわずかである。Digital Scan の試験結果の例を図 6.9 に示す。

図 6.9 Analog Scan の試験結果の例 [17]

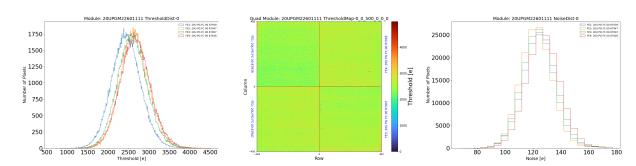

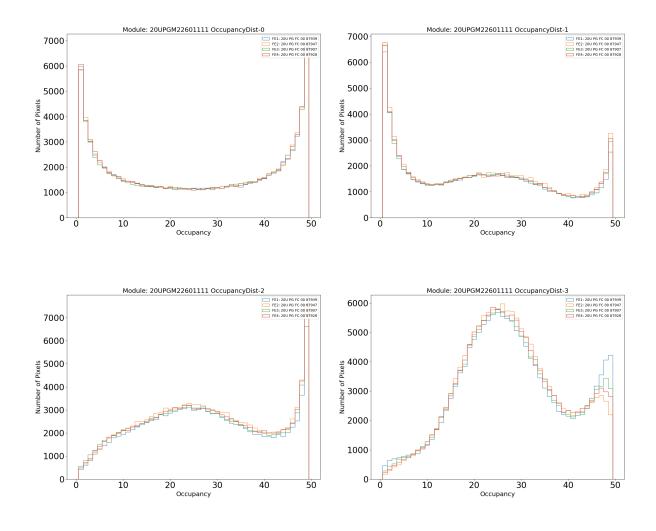

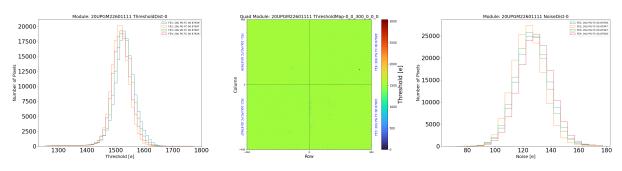

#### • Threshold scan (high range/high definition)

FE チップのアナログ回路にあらかじめ電荷量が既知の試験電荷を入れて Threshold の測定を行う。入力電荷量を変えながら occupancy を測定する。入力電荷量が小さい場合には occupancy は 0% だが、入力電荷量を大きくしていくと、それに従って occupancy が大きくなり、最終的に 100% となる。この時の入力電荷量と occupancy の関係から Threshold の測定を行う。入力電荷量と occupancy の関係は、S 字状になるため、S カーブと呼ばれる。ここで、Threshold は occupancy が 50% となった時の入力電荷量、Noise は S カーブに対して誤差関数をフィットしたときの標準偏差を示す。high range では入力電荷量 0 e-から 5000 e-の間、high definition では 0 e-から 3000 e-の間で 0 S カーブ測定を行う。特に、PFA では、0 そのピクセルの threshold - そのチップの threshold の平均値 0 - 0 200 e-の場合は tuning bad、平均 noise が 0 300 e-以上の場合は high ENC と判定する。測定結果は、Tuning 前と Tuning 後で大きく異なるため、Tuning 前後の試験 結果の例を図 0 6.10、図 0 6.11 に示す。

図 6.10 Tuning 前の Threshold scan の試験結果の例 [17]

図 6.11 Tuning 後の Threshold scan の試験結果の例 [17]

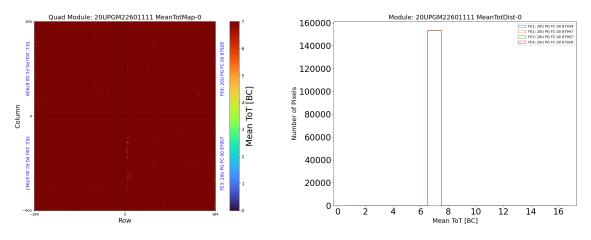

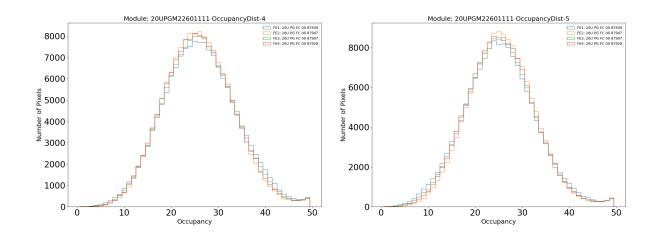

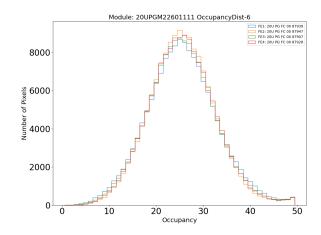

#### · TOT scan

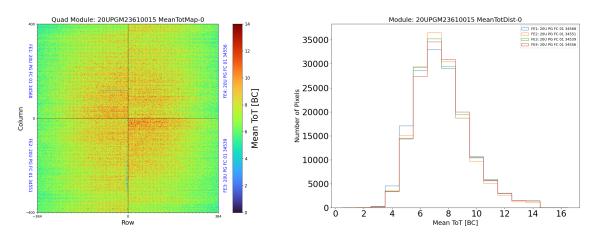

試験電荷を入射して、ToT を計測する。特定の試験電荷 (現在は 6000 e-) を入れたときの TOT (time-overthreshold) 分布を測定する。試験量産においては、TOT が 7 に固定されているため、結果としては常に 7 が 測定される。本量産では、実際にモジュールから測定した TOT を確認できる。TOT Scan の試験量産での結果の例を図 6.12、本量産での結果の例を図 6.13 に示す。

図 6.12 試験量産での TOT scan の試験結果の例 [17]

図 6.13 本量産での TOT scan の試験結果の例 [17]

### · Global threshold (re-)tune

Threshold を調整するために、FE チップには 2 種類の threshold 調整用の DAC が実装されている。global threshold DAC と呼ばれる DAC でチップ全体で共通の threshold 電圧を調整している。また、TDAC と呼ばれる DAC で、ピクセルごとの微調整を行っている。global threshold tuning では、設定したい threshold に等しい試験電荷を入れ、まず、global threshold DAC を変更しながらピクセルごとに occupancy を測定し、occupancy が 50 % 以上のピクセルと 50 % 以下のピクセルが半分ずつになるような値に調整している。Global threshold (re-)tune の試験結果の例を図 6.14 に示す。

図 6.14 Global threshold (re-)tune の試験結果の例 [17]

### • Pixel threshold (re-)tune

この tune は、global threshold tune と同様の操作を行う。この tune の場合は、TDAC の値を変更しながら、occupancy が 50% 以上のピクセルと 50% 以下のピクセルが半分ずつの状態で、そのばらつきができる限り小さくなるように調整を行う。Pixel threshold (re-)tune の試験結果の例を図 6.15 に示す。

図 6.15 Pixel threshold (re-)tune の試験結果の例 [17]

# • TOT tune

6000 e-の試験電荷を入射し、その平均値が TOT = 7 になるように preamp を調整する。TOT tune の試験結果の例を図 6.16 に示す。

図 6.16 TOT tune の試験結果の例 [17]

#### · Noise scan

試験電荷をなにも入れない状態でランダムに 1000 万トリガーを発行し、その時のノイズヒットの数を計測する。PFA では、occupancy が  $10^{-6}$  より大きい場合に noisy と判定する。TOT tune の試験結果の例を図 6.17 に示す。

図 6.17 Noise scan の試験結果の例 [17]

# $\boldsymbol{\cdot}$ Disconnected bump scan

各ピクセルに隣接したピクセルに約約 40000 e-の試験電荷を入射して、ピクセル間のクロストークを利用してバンプ剥がれを検出する。ピクセルがバンプによって正常に接続されている場合、隣接したピクセルへの入

射電荷は、センサーのクロストークを経て、試験したいピクセルでも確認される。バンプの接続に不具合がある場合には、センサー上のクロストークが検出できないため、occupancy の減少が見られる。現在は、試験ピクセルの周囲 8 ピクセルに入射して試験を行っている。Disconnected bump scan の試験結果の例を図 6.18 に示す。

図 6.18 Disconnected bump scan の試験結果の例 [17]

## · Merged bump scan

Threshold を 1500 e-に設定した状態で、隣接したピクセルに試験電荷を 2000 e-を入射する。その後、隣接したピクセルのバンプ同士がショートしている部分を計測する。現在は、試験したいピクセルの上下左右の 4 ピクセルに試験電荷を入射して試験を行っている。ピクセルが正常な場合、2000 e-の試験電荷を入射したときのクロストークは十分に小さいため検出されないが、バンプに不具合があると高い occupancy が測定される。Merged bump scan の試験結果の例を図 6.19 に示す。

図 6.19 Merged bump scan の試験結果の例 [17]

#### · Zero-bias threshold scan

HV を印加しない状態で threshold scan を行う。センサーを空乏化させない場合、センサーのノイズが大きくなるため、バンプが正常なピクセルと不具合が発生しているピクセルにおいて、ノイズが異なることを利用して、バンプの接続状況を確認している。Zero-bias threshold scan の試験結果の例を図 6.20 に示す。

図 6.20 Zero-bias threshold scan の試験結果の例 [17]

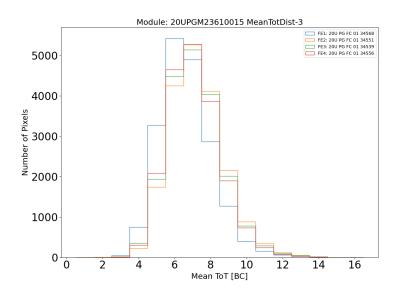

## · Xray scan

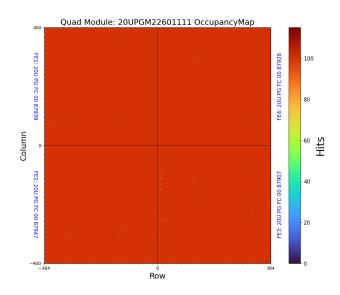

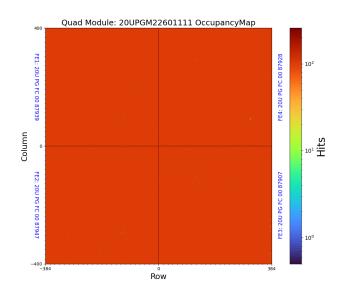

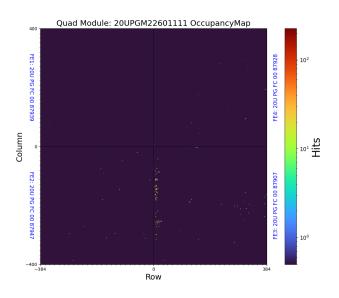

X 線装置でモジュールに X 線を入射し、各ピクセルでのヒット数を確認する。前述の通り、この scan では、 $50 \mathrm{kV}$ 、 $80 \mathrm{uA}$  の X 線を使ってモジュールのバンプ剥がれの確認を行う。X 線装置では、電子を加速して Ag 薄膜に照射することで、 $22.1~\mathrm{keV}$ 、 $25.5~\mathrm{keV}$  の特性 X 線および最大  $50~\mathrm{keV}$  までの制動放射由来の X 線を生成している。X ray scan の試験結果の例を図  $6.21~\mathrm{keV}$  に示す。低エネルギーの X 線であることからモジュールの部品やクーリングボックスの構成要素による吸収も見られるものの、正常にバンプが接続しているピクセルでは、数十のヒット数が確認できる。

図 6.21 Xray scan の試験結果の例 [17]

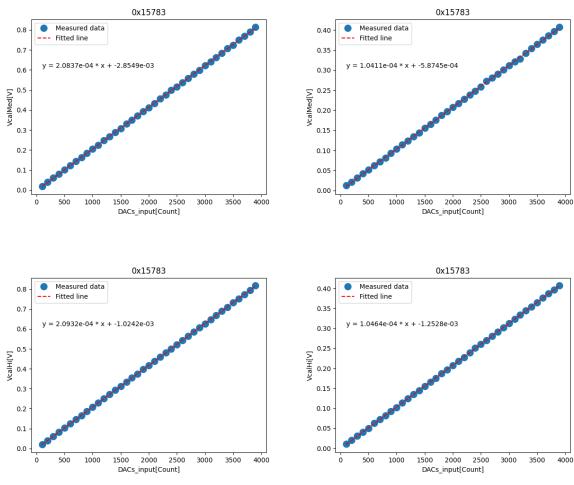

## 6.2 電気回路読み出し試験の結果解析

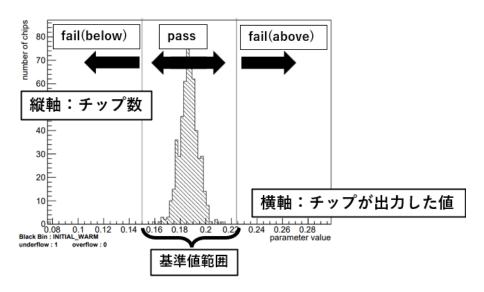

電気回路読み出し試験の結果は、LocalDB に保存され、図 6.1 や図 6.22 のような形で試験結果を確認することができる。Quad モジュールに搭載された 4 つの FE チップそれぞれで試験結果を確認することができるため、試験結果は FE チップごとのものとなっている。つまり、試験結果の数は、試験したモジュールの数の約 4 倍となる。モジュールの状態によって、マスクして試験を行わなかった FE チップも存在するため、試験結果の数は、正確にモジュールの数の 4 倍にはならない。それぞれのパラメータには基準値が設定されており、基準値内の値を出力した FE チップを pass、基準値より大きい値を出力した FE チップを fail(avobe)、基準値より小さい値を出力した FE チップを fail(below) として結果の評価を行っている。試験を行った FE チップの結果の定義を図 6.23 に示す。図 6.23 において、横軸は各 FE チップが出力した試験結果(単位はパラメータごとに異なる)を、縦軸はそのビン範囲に含まれる結果を出力した FE チップの数を表しており、図中の 2 本の縦線は、そのパラメータの基準値の範囲を表している。本研究では、電気回路読み出し試験のうち、simple scan の結果解析を行った。現在、simple scan で調べているパラメータ数は約 70 ほど存在しており、それらのパラメータについて、時系列での傾向や fail モジュールの割合などを確認している。

Parameter Analysis result QC criteria Pass ADC\_CALIBRATION\_SLOPE 0.175 [0.15, 0.224] True ADC\_CALIBRATION\_OFFSET 12.0 [-9, 31]True ADC\_CALIBRATION\_LINEARITY 1.0 [0.0, 4.0] True

0.02

[0.015, 0.023]

True

ADC\_CALIBRATION for 0x15927

図 6.22 電気回路読み出し試験結果の例

ADC\_ANAGND30\_MEAN

図 6.23 FE チップの読み出し試験結果の定義

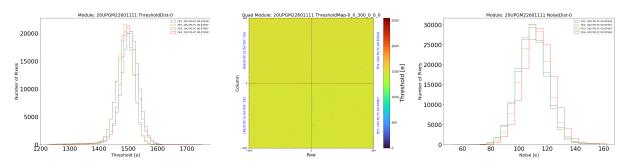

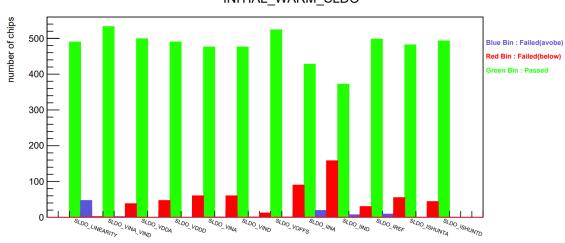

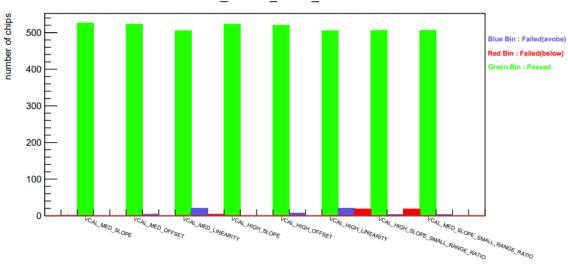

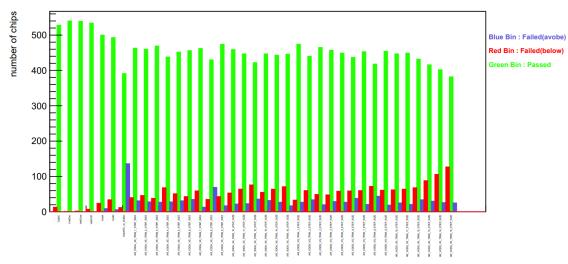

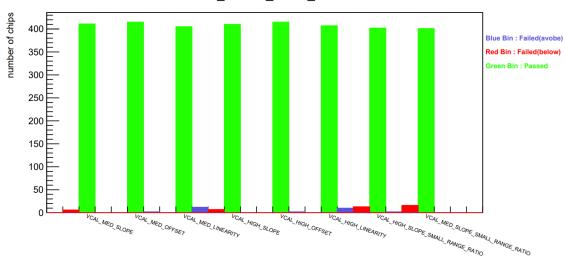

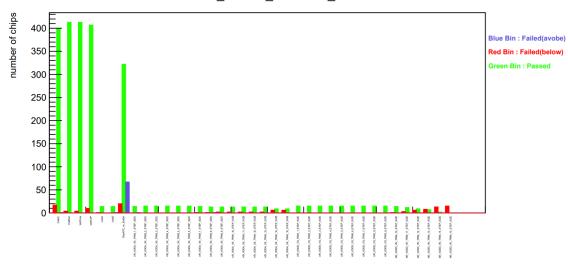

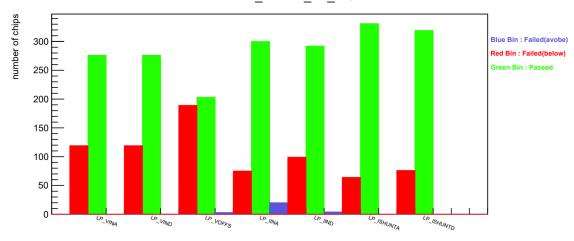

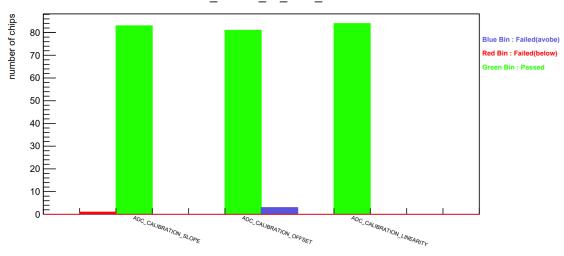

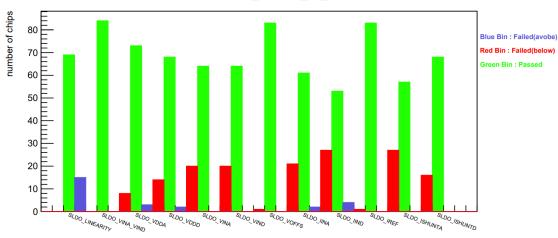

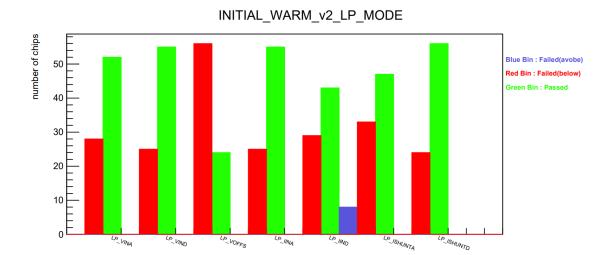

読み出し試験は、5.1 に示すモジュールの量産の流れにおいて、主にワイヤボンディング直後 (Initial stage)、パリレンコーティング直後 (Post Palylene stage)、耐久試験後 (Final stage) に行われる。また、前述の通り、読み出し試験は 20 °Cの warm テスト、-15 °Cの cold テストの 2 種が行われる。本研究では主に、試験量産における warm テストでのワイヤボンディング直後と耐久試験後の読み出し試験の結果解析と本量産における warm テストでのワイヤボンディング直後の読み出し試験の結果解析を行った。本量産に関しては、開始してからまだ日が浅いため、耐久試験等の試験結果が得られていないことから、ワイヤボンディング直後の試験結果を主に扱う。試験の過程において、チップのマスク等が行われることもあるため、後のステージで試験されるチップ数は、前のステージに比べて減少する。まず、各パラメータ群ごとに試験結果をまとめたプロットを、図 6.24、図 6.25、図 6.26 に示す。図 6.24 ~ 6.26 において、横軸はパラメータ名、縦軸はチップ数を表している。また、緑色のビンは基準値内の値を出力した pass チップ、青色のビンは基準値より大きい値を出力した fail(avobe) チップ、赤色のビンは基準値より小さい値を出力した fail(below) チップの数を表している。これらの試験結果から、特に SLDO、Analog readback の一部、LP mode のパラメータにおいて、fail となったチップが見られる。

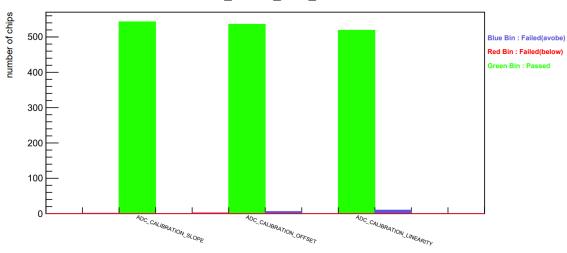

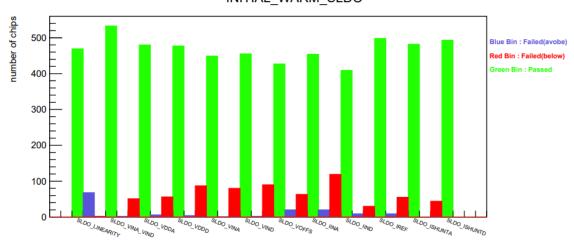

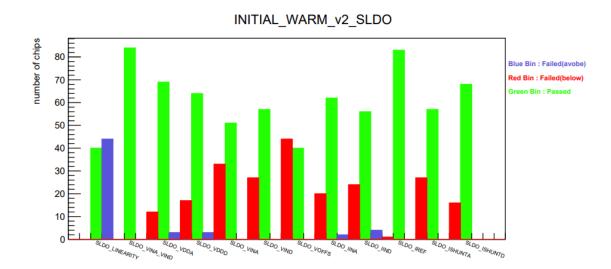

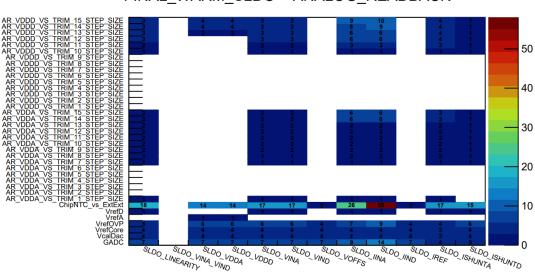

図 6.24 に示される試験量産のワイヤボンディング直後 (Initial stage) の試験結果から、この stage では、ADC calibration と Vcal calibration における電気回路読み出し試験の結果における pass チップの割合が大きいことが分かる。割合としては、全てのパラメータで、約 5 % 未満に fail チップの割合が収まっている。一方、Analog readback、SLDO、LP mode については、基準値を外れた fail チップが目立つことが分かる。特に SLDO では、fail チップが全体の約 30 % を占めるパラメータも出ている。

# INITIAL\_WARM\_ADC\_CALIBRATION

# INITIAL\_WARM\_SLDO

# INITIAL\_WARM\_VCAL\_CALIBRATION

## INITIAL\_WARM\_ANALOG\_READBACK

## INITIAL\_WARM\_LP\_MODE

図 6.24 試験量産での Initial stage における pass チップ、fail チップの割合

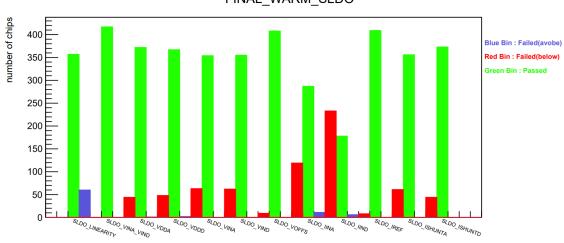

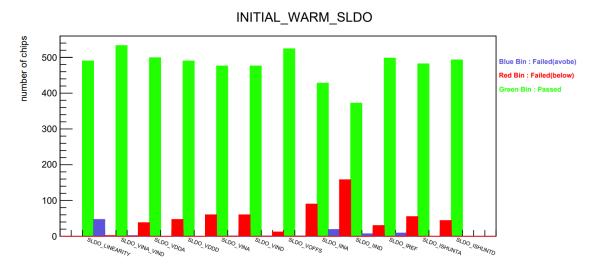

続けて、図 6.25 で示される試験量産の耐久試験後 (Final stage) の電気回路読み出し試験の結果について述べる。試験量産の Initial stage のものと同様に、ADC calibration、Vcal calibration では、fail チップの割合が品質管理試験を通して、低く推移していることが分かる。SLDO と LP mode についても、Initial stage のものと同様で、fail チップの割合が大きいパラメータが存在しており、fail チップの数が pass チップの数を超えているパラメータが見られる。

# FINAL\_WARM\_ADC\_CALIBRATION

# FINAL\_WARM\_SLDO

# FINAL\_WARM\_VCAL\_CALIBRATION

## FINAL WARM ANALOG READBACK

## FINAL\_WARM\_LP\_MODE

図 6.25 試験量産での Final stage における pass チップ、fail チップの割合

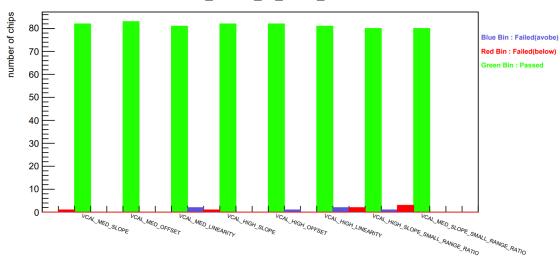

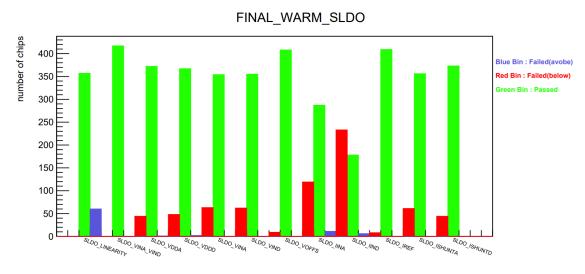

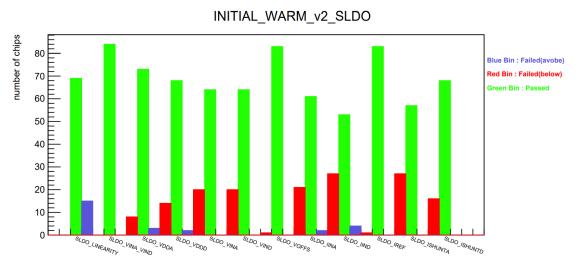

図 6.26 で示される本量産の Initial stage での読み出し試験の結果も確認すると、ADC calibration と Vcal calibration については、前の 2 つと同じく pass チップの割合を高く保っている。このことから、今後の本量産についても、それほど現行の試験手法や基準値に留意せず、引き続き読み出し試験を行うことができると考える。しかし、特に SLDO と LP mode については、fail となるチップ数が多いことが見て取れる。現在、本量産が始まってから日が浅く、試験したモジュールの量が少ないため、基準値を外れたチップが全体から見た割合に影響しやすいことを念頭に置く必要はあるものの、約  $50\sim60~\%$  の割合で fail チップが見られるパラメータも存在している。

特に、図 6.24、図 6.25 については、品質管理試験過程における要因によって、fail となるチップが増えたと考えられる。試験量産における電気回路読み出し試験では、基準値から大きく外れていないモジュールについては、一度次の過程に進めて様子を見るという形で試験を行っていた。その結果、Final stage において、試験の序盤で fail と判断されたチップに加え、試験過程で何らかの理由で問題が発生したチップが fail チップと

判断されたのだと考える。ここで、最初に fail となったパラメータが、モジュールに電源電圧を供給している SLDO に関するものだった場合などは、品質管理試験の過程でモジュールの品質がさらに悪化し、後の試験に 悪影響を及ぼす可能性が考えられる。図 6.26 で示される本量産でも、SLDO において、多くの fail チップが 見られているため、本量産の Final stage では、低い歩留まりになる可能性がある。今後、約 3000 台の量産 を行う中で、効率的に量産を行うためにも、基準値の変更等何らかの対策が必要であると考える。

## INITIAL\_WARM\_v2\_ADC\_CALIBRATION

## INITIAL\_WARM\_v2\_SLDO

# INITIAL\_WARM\_v2\_VCAL\_CALIBRATION

# INITIAL\_WARM\_v2\_ANALOG\_READBACK

図 6.26 本量産での Initial stage における pass チップ、fail チップの割合

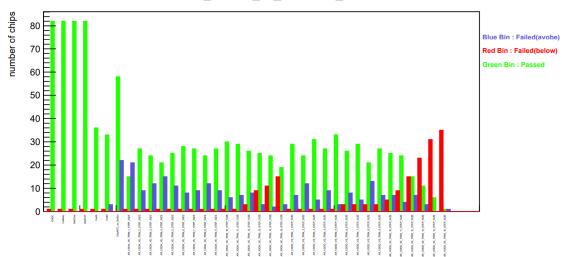

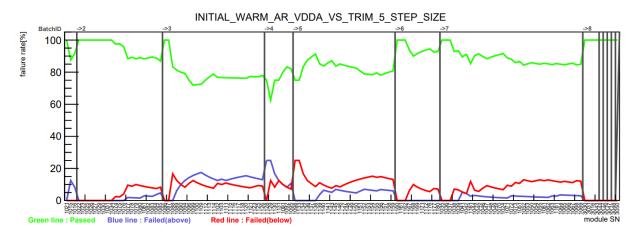

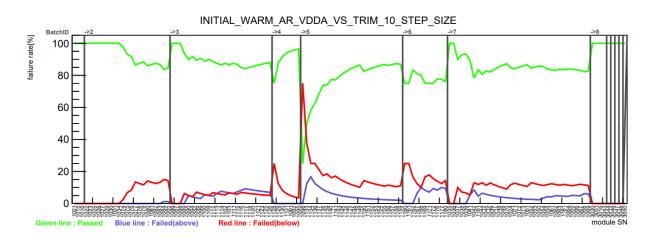

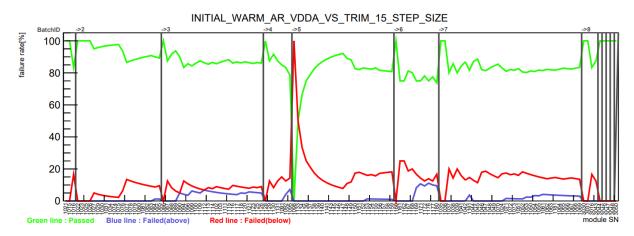

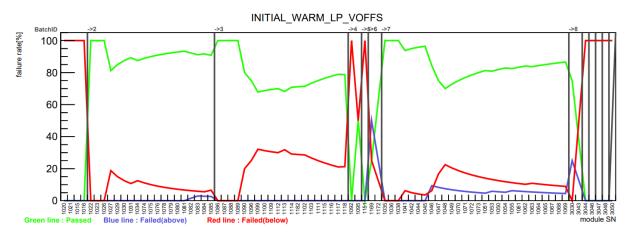

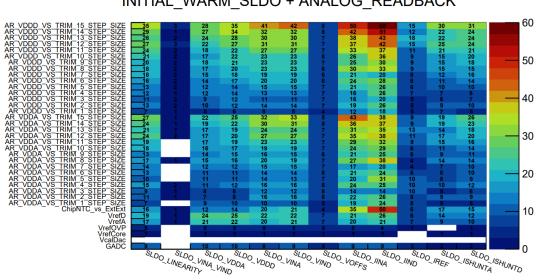

次に、試験結果をセンサーのバッチごとに時系列順で表したものを図 6.27~図 6.31 に示す。ここで、横軸はモジュールのシリアルナンバー、縦軸は全体にチップ数に対する割合を表している。図中の縦線はモジュールの batch ごとの区切りを表している。緑色の線は基準値内の値を出力した pass チップ、青色の線は基準値より大きい値を出力した fail(avobe) チップ、赤色の線は基準値より小さい値を出力した fail(below) チップの全体のチップ数に対する割合を表している。バッチごとに割合を初期化しているため、各バッチの区切りの直後には割合の変動が大きくなる。また、約70のパラメータを見ていることから、全てのパラメータについて結果を示すことはできないため、特徴的なパラメータの結果についてのみ示す。ここでは、試験量産の Initial stage の試験での結果を示している。

これらの時系列での試験結果の変動から、各パラメータについての傾向が見られる。図 6.24 も併せて考えると、ADC calibration と Vcal calibration のパラメータについては、他のパラメータと比べて pass チップの割合が多く、安定した試験であると言える。SLDO については、時系列順に見ても fail チップの割合が高い状態で推移しており、不安定な試験であると考えられる。LP mode も SLDO に近い試験を条件を変えて行っているため、SLDO と同様の不安定な傾向が見られる。また、Analog readback については、pass チップの割合が多いパラメータも存在するものの ADC 値を変えながらの VDDD、A の測定については、fail チップの割合が多く見られ、ADC 値を増やしていくとそれに従って fail チップの割合が多くなる傾向が見られる。

図 6.27 ADC CALIBRATION OFFSET の pass チップ、fail チップの時系列変化

また、図 6.28 や図 6.30 で見られるように、基準値を外れ、fail となるチップが多いパラメータについても、常に試験結果が悪い状態ではないことが分かる。これらの図は、モジュールに用いるシリコンセンサーのバッチごとに区切られているため、特定のバッチで fail となるチップが見られる傾向があることが分かる。このことから、今後の本量産においても、バッチごとに品質管理試験の結果をまとめ、歩留まりが良いバッチと悪いバッチを分類することで、高品質な試験を行うことができると考える。

図 6.28 SLDO IIND の pass チップ、fail チップの時系列変化

図 6.29 VCAL HIGH OFFSET の pass チップ、fail チップの時系列変化

図 6.30 AR VDDA VS TRIM STEP SIZE の DAC 値ごとの pass チップ、fail チップの時系列変化

図 6.31 LP VOFFS の pass チップ、fail チップの時系列変化

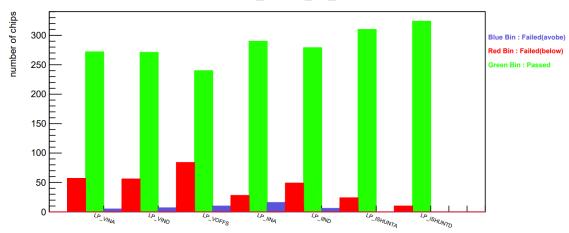

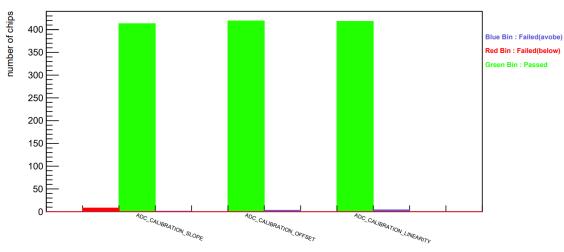

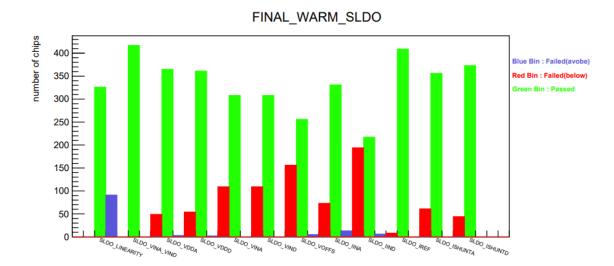

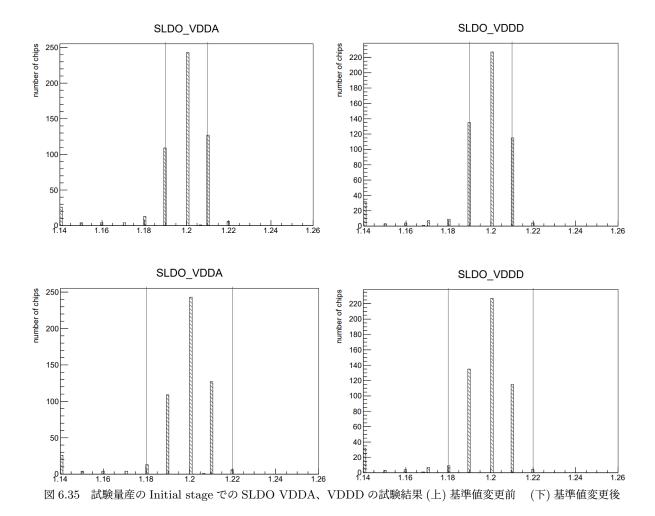

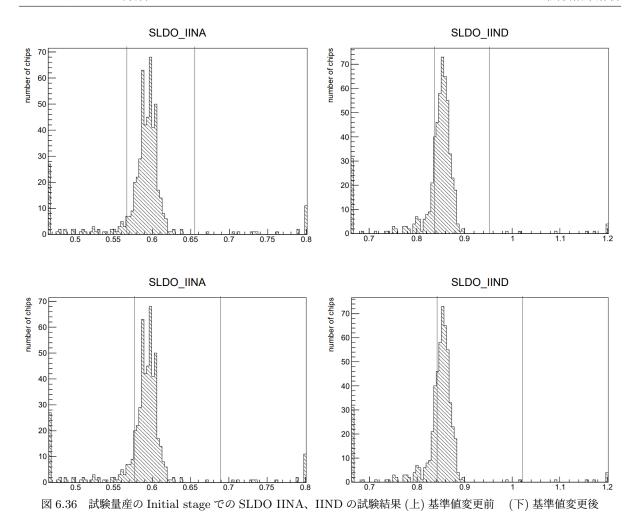

また、2024 年 11 月ごろにバークレーにおいて、12 ある SLDO 試験のパラメータのうち、8 つのパラメータの基準値が変更された。この変更は、試験量産の結果やシミュレーション等を踏まえて行われ、モジュールの性能を損ねない範囲で変更が行われた。日本における量産についても、この変更された基準値を採用して

いる。基準値更新された基準値について、表 6.1 に示す。また、変更前後の SLDO パラメータにおける pass チップ、fail チップの割合を図 6.33~図 6.34 に示す。この基準値変更により、fail チップの割合が減少する パラメータが見られ、試験量産の 2 ステージ、本量産どちらでも減少していることが分かる。一方、SLDO IINA と SLDO IIND の 2 つのパラメータに関しては、3 つのプロット全てにおいて、ほぼ fail チップの割合が改善していないことが分かる。また、図 6.23 と同様に、試験量産の Initial stage での基準値変更前後の SLDO 試験における読み出し試験結果を示したものを、図 6.35、図 6.36 に示す。図 6.35 では、基準値の変更 で結果が改善したパラメータである SLDO VDDA、VDDD について表している。これらのパラメータでは、基準値の範囲が拡大しており、変更の結果として pass チップが増加している。一方、図 6.36 では、基準値の変更によって改善が見られなかった SLDO IINA、IIND について表している。これらのパラメータでは、読み出し試験の結果において左側にテールが見られるにも関わらず、右側に基準値範囲がシフトしている様子が見られる。その結果として、基準値に収まる pass チップ数が減少している。以上より、fail チップが減少した6つのパラメータの基準値については、今後の本量産においても妥当性を確認した上で引き続き用いることができると考えられる。しかし、SLDO IINA と SLDO IIND については、基準値を変更したにも関わらず結果が改善していないため、今後の試験にこの基準値を用いるかについては、議論が必要であると考える。また、より妥当な基準値はないかを考察することも必要である。

| 変更前基準値            | 変更後基準値                                                                                                               |

|-------------------|----------------------------------------------------------------------------------------------------------------------|

| [0.0, 0.035]      | [-0.09, 0.09]                                                                                                        |

| [1.19, 1.21]      | [1.18, 1.22]                                                                                                         |

| [1.19, 1.21]      | [1.18, 1.22]                                                                                                         |

| $[1.452,\ 1.524]$ | [1.427,  1.603]                                                                                                      |

| [1.452,1.524]     | [1.427,  1.603]                                                                                                      |

| [0.979,  1.001]   | [0.93,  1.03]                                                                                                        |

| [0.567,0.655]     | [0.5769,0.689]                                                                                                       |

| [0.837,  0.952]   | [0.842,  1.022]                                                                                                      |

|                   | [0.0, 0.035]<br>[1.19, 1.21]<br>[1.19, 1.21]<br>[1.452, 1.524]<br>[1.452, 1.524]<br>[0.979, 1.001]<br>[0.567, 0.655] |

表 6.1 変更前後の SLDO パラメータの基準値

## INITIAL WARM SLDO

図 6.32 試験量産での Initial stage における各チップの割合 (上) 基準値変更前 (下) 基準値変更後

図 6.33 試験量産での Final stage における各チップの割合 (上) 基準値変更前 (下) 基準値変更後

図 6.34 本量産での Initial stage における各チップの割合 (上) 基準値変更前 (下) 基準値変更後

# 6.3 パラメータの分類

電気回路読み出し試験では、全 67 パラメータについて見ている。そのパラメータの一覧を表 6.2 に示す。図 6.24 などから分かるように、SLDO などのパラメータ群で試験を fail したパラメータが多く見られている。そのため、fail したチップの割合から各パラメータを分類した。図 6.24~6.26 から考え、読み出し試験で fail と判定されたチップの数の割合でパラメータを分類したものを、表 6.3 で示す。ここで、fail チップの割合は、基準値より大きかったもの (avobe)、小さかったもの (below) をまとめて考えている。

ADC calibration Analog readback SLDO Vcal calibration LP mode VINA LINEARITY SLOPE GADC MED SLOPE OFFSET MED OFFSET MED LINEARITY VcalDac VINA VIND VIND LINEARITY VOFFS VDDA VrefCore VrefOVP VDDD HIGH SLOPE IINA VINA HIGH OFFSET IIND VrefA VrefD VIND HIGH LINEARITY ISHUNTA ChipNTC vs ExtExt VDDA VS TRIM 1 STEP SIZE VOFFS HIGH SLOPE SMALL RANGE RATIO ISHUNTD IINA MED SLOPE SMALL RANGE RATIO VDDA VS TRIM 2 STEP SIZE VDDA VS TRIM 3 STEP SIZE HND IREF VDDA VS TRIM 4 STEP SIZE ISHUNTA VDDA VS TRIM 5 STEP SIZE ISHUNTD VDDA VS TRIM 6 STEP SIZE VDDA VS TRIM 7 STEP SIZE VDDA VS TRIM 8 STEP SIZE VDDA VS TRIM 9 STEP SIZE VDDA VS TRIM 10 STEP SIZE VDDA VS TRIM 11 STEP SIZE VDDA VS TRIM 12 STEP SIZE VDDA VS TRIM 13 STEP SIZE VDDA VS TRIM 14 STEP SIZE VDDA VS TRIM 15 STEP SIZE VDDD VS TRIM 1 STEP SIZE VDDD VS TRIM 2 STEP SIZE VDDD VS TRIM 3 STEP SIZE VDDD VS TRIM 4 STEP SIZE VDDD VS TRIM 5 STEP SIZE VDDD VS TRIM 6 STEP SIZE VDDD VS TRIM 7 STEP SIZE VDDD VS TRIM 8 STEP SIZE VDDD VS TRIM 9 STEP SIZE VDDD VS TRIM 10 STEP SIZE VDDD VS TRIM 11 STEP SIZE VDDD VS TRIM 12 STEP SIZE VDDD VS TRIM 13 STEP SIZE

表 6.2 現在、電気回路読み出し試験において試験結果の解析をしているパラメータの一覧

表 6.3 から、試験量産の Initial stage から、本量産の Final stage まで、時間が経過するたびに fail チップが多く確認されるパラメータの数が増えていることが分かる。これらの分類から、読み出し試験で fail となったチップは、品質管理試験の中で、同じモジュールのチップに悪影響を及ぼし、歩留まりを低下させる要因なのではないかと考えた。試験量産と本量産で試験されるモジュールは異なるため、本量産におけるパラメータの分類については、別の要因が考えられ得るものの、現状多くの fail チップが見られるため、今後の試験手法や基準値の妥当性の検証は必要である。

VDDD VS TRIM 14 STEP SIZE VDDD VS TRIM 15 STEP SIZE

表 6.3 fail チップの割合によるパラメータの分類

|                       | 試験量産の Initial stage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 試験量産の Final stage                                                                                                                                                                                                                                                                                                                 | 本量産の Initial stage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| fail chip $>10~\%$    | AR VDDA VS TRIM 1 STEP SIZE AR VDDA VS TRIM 2 STEP SIZE AR VDDA VS TRIM 3 STEP SIZE AR VDDA VS TRIM 3 STEP SIZE AR VDDA VS TRIM 4 STEP SIZE AR VDDA VS TRIM 5 STEP SIZE AR VDDA VS TRIM 5 STEP SIZE AR VDDA VS TRIM 6 STEP SIZE AR VDDA VS TRIM 8 STEP SIZE AR VDDA VS TRIM 8 STEP SIZE AR VDDA VS TRIM 10 STEP SIZE AR VDDA VS TRIM 10 STEP SIZE AR VDDA VS TRIM 11 STEP SIZE AR VDDA VS TRIM 12 STEP SIZE AR VDDA VS TRIM 13 STEP SIZE AR VDDA VS TRIM 15 STEP SIZE AR VDDD VS TRIM 15 STEP SIZE AR VDDD VS TRIM 15 STEP SIZE AR VDDD VS TRIM 5 STEP SIZE AR VDDD VS TRIM 6 STEP SIZE AR VDDD VS TRIM 6 STEP SIZE AR VDDD VS TRIM 7 STEP SIZE AR VDDD VS TRIM 8 STEP SIZE AR VDDD VS TRIM 8 STEP SIZE AR VDDD VS TRIM 9 STEP SIZE AR VDDD VS TRIM 10 STEP SIZE AR VDDD VS TRIM 11 STEP SIZE AR VDDD VS TRIM 12 STEP SIZE AR VDDD VS TRIM 13 STEP SIZE AR VDDD VS TRIM 14 STEP SIZE SLDO LINEARITY SLDO VDDA SLDO VDDA SLDO VDDD SLDO VDD SLDO VINA SLDO ISHUNTA SLDO ISHUNTD LP mode UND LP mode INNA LP mode ISHUNTA | SLDO LINEARITY SLDO VDDA SLDO VDDD SLDO VINA SLDO UIND SLDO ISHUNTA SLDO ISHUNTA LP mode ISHUNTA LP mode ISHUNTD                                                                                                                                                                                                                  | AR VDDA VS TRIM 10 STEP SIZE AR VDDD VS TRIM 3 STEP SIZE AR VDDD VS TRIM 5 STEP SIZE SLDO LINEARITY SLDO VDDA SLDO VDDD SLDO ISHUNTD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| fail chip $>$ 20 $\%$ | AR ChipNTC vs ExtExt<br>AR VDDD VS TRIM 15 STEP SIZE<br>SLDO IINA<br>SLDO IIND<br>LP mode VOFFS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | AR ChipNTC vs ExtExt AR VDDA VS TRIM 14 STEP SIZE AR VDDA VS TRIM 15 STEP SIZE AR VDDD VS TRIM 12 STEP SIZE AR VDDD VS TRIM 12 STEP SIZE AR VDDD VS TRIM 13 STEP SIZE AR VDDD VS TRIM 14 STEP SIZE AR VDDD VS TRIM 15 STEP SIZE SLDO IINA SLDO IIND LP mode VINA LP mode VIND LP mode VIND LP mode VIND LP mode IINA LP mode IINA | AR ChipNTC vs ExtExt AR VDDA VS TRIM 1 STEP SIZE AR VDDA VS TRIM 2 STEP SIZE AR VDDA VS TRIM 3 STEP SIZE AR VDDA VS TRIM 3 STEP SIZE AR VDDA VS TRIM 5 STEP SIZE AR VDDA VS TRIM 5 STEP SIZE AR VDDA VS TRIM 6 STEP SIZE AR VDDA VS TRIM 7 STEP SIZE AR VDDA VS TRIM 7 STEP SIZE AR VDDA VS TRIM 9 STEP SIZE AR VDDA VS TRIM 9 STEP SIZE AR VDDA VS TRIM 11 STEP SIZE AR VDDA VS TRIM 11 STEP SIZE AR VDDA VS TRIM 12 STEP SIZE AR VDDA VS TRIM 15 STEP SIZE AR VDDD VS TRIM 15 STEP SIZE AR VDDD VS TRIM 5 STEP SIZE AR VDDD VS TRIM 5 STEP SIZE AR VDDD VS TRIM 6 STEP SIZE AR VDDD VS TRIM 7 STEP SIZE AR VDDD VS TRIM 8 STEP SIZE AR VDDD VS TRIM 9 STEP SIZE AR VDDD VS TRIM 10 STEP SIZE AR VDDD VS TRIM 11 STEP SIZE AR VDDD VS TRIM 12 STEP SIZE AR VDDD VS TRIM 15 STEP SIZE AR VDDD VS TRIM 14 STEP SIZE AR VDDD VS TRIM 15 STEP SIZE AR VDDO VINA SLDO IINA SLDO IINA SLDO IINA SLDO IINA LP mode VIND LP mode VIND LP mode IINA LP mode IINA LP mode IINA LP mode ISHUNTA LP mode ISHUNTA LP mode ISHUNTA |

#### 6.4 fail チップの原因

前述の通り、読み出し試験において基準値外と判定され、fail チップとなったものは、同じモジュールのチップに悪影響を及ぼし、後の試験での fail チップ割合増加の要因になっていると考える。モジュールに電源電圧を印加する SLDO やモジュールの各回路への電源供給の状態を確認する Analog readback などの機器に不具合がある場合、実際のモジュールの動作にも少なからず悪影響があると考えられる。そこで、fail チップ

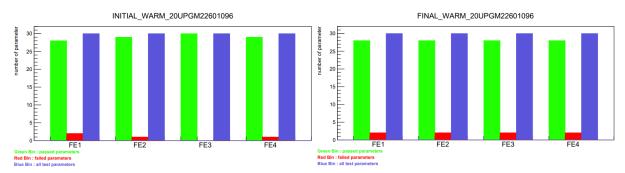

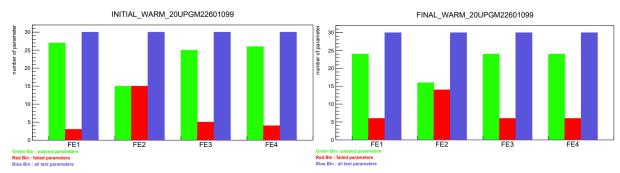

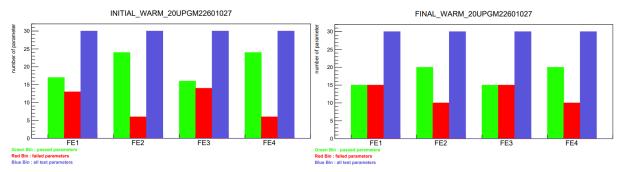

の影響を確認するため、モジュールの各チップごとの fail パラメータ数をまとめた図を、図 6.37~図 6.39 に示す。ここで、横軸はチップ番号、縦軸はパラメータの数を表している。また、緑色のビンは試験結果が pass のパラメータ数、赤色のビンは試験結果が fail のパラメータ数、青色のビンはそのチップが行った総試験数を表している。これらは、試験量産での試験結果である。図 6.37 から、Initial stage において良い試験結果が出ていると、Final stage でも同様の傾向が見られている。一方、図 6.38、図 6.37 から、Initial stage において、fail となったパラメータ数が多い場合、Final stage でより多くのパラメータの試験結果が fail となっている。Initial stage での結果が悪いほど、Final stage がより悪化しているように見える。ここに示した図は、試験量産されたモジュールのうちのわずかなものだが、他のモジュールも同様の傾向を示している。

図 6.37 モジュール番号 20UPGM22601096 のチップごとの試験結果 (左)Initial stage (右)Final stage

図 6.38 モジュール番号 20UPGM22601099 のチップごとの試験結果 (左)Initial stage (右)Final stage

図 6.39 モジュール番号 20UPGM22601027 のチップごとの試験結果 (左)Initial stage (右)Final stage

以上より、読み出し試験の結果が安定していたものはその後も安定し、そうでないものは後の試験で fail と

なるパラメータが多くなると考えられる。そのため、今後の試験の高効率化、高品質化のために、読み出し試験において、一定数以上のパラメータで fail となったものは、それまでの試験で得られた結果に関わらず取り除く等の措置が有効であると考える。また、特定の試験で一定値以上基準値から外れたものを分別することにより、高い歩留まりでの量産が行えるのではないかと考えた。

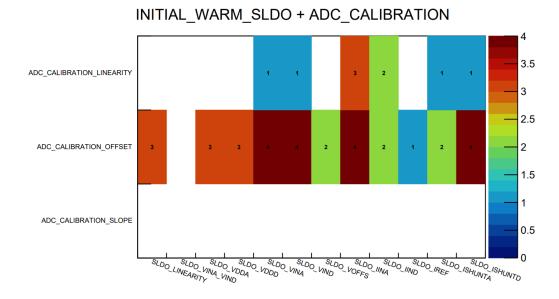

次に、SLDO を始めとした特定のパラメータの不具合によって発生している fail チップについて調べるため、試験量産での試験結果から各パラメータごとの相関を調べた。パラメータごとの fail チップの相関を図  $6.40\sim$ 図 6.44 に示す。図  $6.40\sim$ 図 6.44 は、SLDO の各パラメータとそれ以外のパラメータについて表している。これらの図において、横軸と縦軸はパラメータ名、数値はそれらのパラメータが同時に fail となったチップの数を表している。空白の部分は、2 つのパラメータで同時に fail となったチップが 1 つも存在しないことを表している。

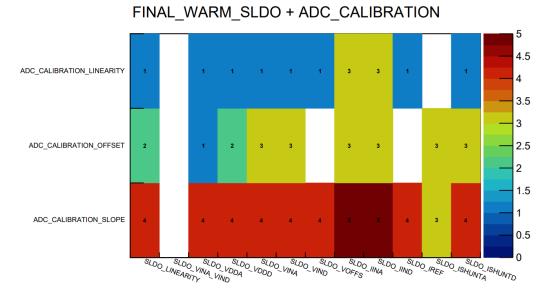

図 6.40 に示す SLDO と ADC calibration における fail チップの相関においては、全体的に同時に fail となるチップが少ないことが分かる。これは、図 6.24 などから分かるように、ADC calibration 試験において、そもそも fail チップが少ないことが原因だと考えられる。

73

図 6.40 試験量産での SLDO と ADC calibration における fail チップ相関 (上)Initial stage (下)Final stage

図 6.41 に示す SLDO 内での他の各パラメータとの相関においては、他のパラメータとの相関に比べ、多くの fail チップがあることが分かる。Initial stage と Final stage での相関を比較すると、全体的に 10 個程度 fail となるチップ数が増加している。特に、SLDO IINA、IIND といったパラメータに関連している部分では、 $20\sim30$  個ほど 2 つのパラメータで同時に fail となるチップ数が増えていることが分かる。

INITIAL\_WARM\_SLDO + SLDO

## FINAL\_WARM\_SLDO + SLDO

図 6.41 試験量産での SLDO の各パラメータにおける fail チップ相関 (上)Initial stage (下)Final stage

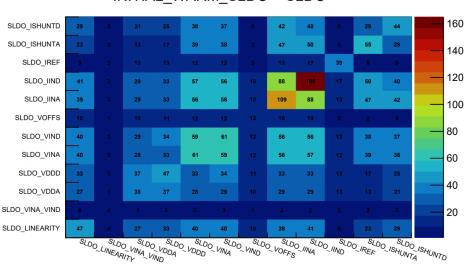

図 6.42 に示す SLDO と Analog readback との相関においては、多くの fail チップが確認できる。特に、 SLDO IINA や IIND と関連した際に、同時に fail となるチップが多い傾向が見られる。

### INITIAL\_WARM\_SLDO + ANALOG\_READBACK

### FINAL\_WARM\_SLDO + ANALOG\_READBACK

図 6.42 試験量産での SLDO と Analog readback における fail チップ相関 (上)Initial stage (下)Final stage

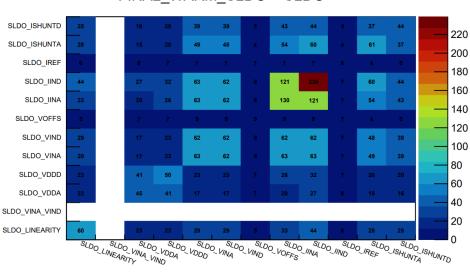

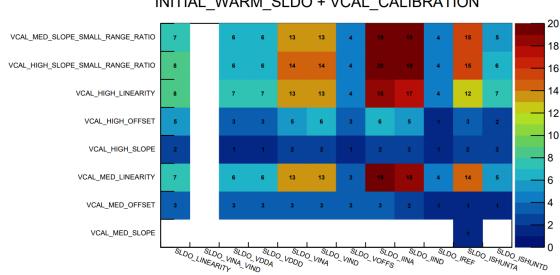

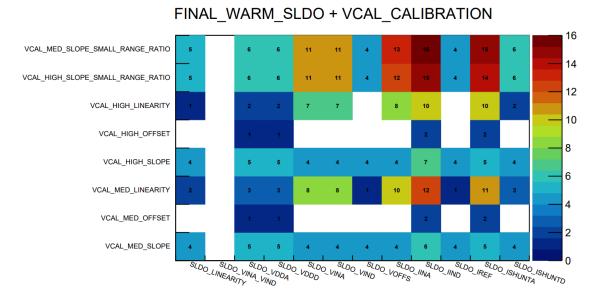

図 6.43 に示す SLDO と Vcal calibration との相関においては、SLDO と ADC calibration の相関と同様 に、全体的に同時に fail となるチップの数が少ないことが分かる。こちらの原因についても、図 6.24 から分 かるように、Vcal calibration において、fail チップの数がそもそも少ないことが原因だと考えられる。しか し、SLDO IINA、IIND のパラメータにおいて、20 個弱の fail チップが見られるパラメータも存在している。

### INITIAL\_WARM\_SLDO + VCAL\_CALIBRATION

図 6.43 試験量産での SLDO と Vcal calibration における fail チップ相関 (上)Initial stage (下)Final stage

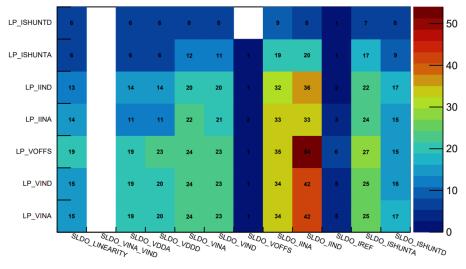

図 6.44 に示す SLDO と LP mode との相関においては、図 6.24 などから分かるように、LP mode では多くの fail チップが確認されていることから、SLDO と同時に fail となったチップが多く見られた。Initial stage と Final stage での相関を比較すると、図 6.41 で示される SLDO 内のパラメータ同士の相関と同様に、全体的に 10 個程度同時に fail となるチップの数が増加していることが分かる。最も多く増加しているのは、SLDO IIND と LP VOFFS を同時に fail となったチップで、約 50 個増えている。

# INITIAL\_WARM\_SLDO + LP\_MODE

#### LP\_ISHUNTD 100 LP\_ISHUNTA 25 80 LP\_IIND 60 LP\_IINA LP VOFFS 40 20 LP VINA 43 n SLDO\_LINEARITY SLDO\_ISHUNTD \$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V\$LDO\_V

#### FINAL\_WARM\_SLDO + LP\_MODE

図 6.44 試験量産での SLDO と LP mode における fail チップ相関 (上)Initial stage (下)Final stage

以上では、SLDO 内の特定のパラメータに関する試験で fail と判定されたチップが、他のチップに悪影響を 及ぼしていると考え、試験量産での試験結果から各パラメータごとの相関を調べた。結果として、そもそも図 6.24 など、fail と判定されたチップの割合が少ないパラメータに関しては、他のパラメータと同時に fail して いるチップの数は少ない傾向が見られた。一方で、fail となったチップの数が多いパラメータに関しては、他 のパラメータでの fail 判定と関連がある傾向が確認できた。特に、SLDO の IINA、IIND というパラメータ に関しては、他のパラメータと同時に fail となっていることが多かった。加えて、Initial stage と Final stage での相関を比較した際に、これらのパラメータに関連したパラメータにおいて、2 つのパラメータで同時に fail となるチップの数の増加が多く見られた。これらのパラメータは、SLDO レギュレータへの入力電流につ いて表しているため、これらの試験において、fail 判定が出ているということは、モジュールの電源電流に関 する部分で不具合が生じていることを示している。そのため、IINA、IIND が fail となったチップについて は、モジュールの電源の状態が不安定な状態で他の試験が行われていたと考えられ、これが相関に見た際に2 つのパラメータで同時に fail と判定されるチップの多さに繋がっていると考えられる。よって、他のパラメー タの試験への影響を低減するために、SLDO の IINA、IIND パラメータに関しては、基準値の変更が必要で あると考えられる。前述の通り、先日、表 6.1 で示すように基準値が変更されたが、SLDO IINA、IIND に関 しては、ほとんど影響が見られなかった。そのため、今後の試験の効率化、高品質化のために、この2つのパ ラメータについての改善は急務である。また、図 6.44 における SLDO IIND と LP mode VOFFS などで見 られるように、特定のパラメータ間に相関があることが分かる。これは、それらのパラメータ間に何らかの因 果関係があることを示唆していると考えられる。そのため、複数のパラメータにおいて fail と判定されたチッ プについても、根本的な原因を特定、除去すれば fail となるパラメータ数が減少する可能性がある。よって、 チップの本質的な不具合の要因を調べ、取り除くことのできるアルゴリズムの準備が必要であると考える。

ただし、現在、試験量産、本量産を通して全ての電気回路読み出し試験を合格したモジュールは 0 台であるので、今後の本量産に向けて、柔軟に基準値や試験手法等を定義していく必要があると考える。また、読み出し試験におけるチップの不具合は、図 4.2 で示すような試験用機器が原因である可能性も存在するため、試験のためのハードウェアについても検証が必要である。

#### 7 まとめと展望

CERN での LHC-ATLAS 実験は、2020 年代後半にかけて、HL-LHC 実験へのアップグレードが計画されている。この増強に従って、現行の内部飛跡検出器が、ITk と呼ばれるシリコン半導体検出器に置換される。そのため、ITk モジュールは世界中で約 10000 台の量産が予定されており、日本ではそのうち 3000 台を製造することとなっている。このモジュールの製造にあたって、検出器の組み立てや品質管理試験が行われる。 2023 年 6 月から試験量産が始まり約 150 台が製造され、2024 年 10 月からは本格的な量産が始まっている。本量産において製造されるモジュールは実際に HL-LHC 実験に用いられるため、試験量産で得られた経験や情報をもとに高精度で量産を行う必要がある。そのため、本研究では、品質管理試験のうち試験量産と本量産の電気回路読み出し試験の結果解析を行い、本量産における試験効率化や高品質化を目指した。

結果解析は、試験量産および本量産で得られた読み出し試験の結果をデータベースから取り出し、時系列での試験結果の傾向変化や基準値を満たさなかったチップの割合などを調べることにより行った。読み出し試験は、約70のパラメータについて調べている。解析の結果として、約50のパラメータにおいて、基準値を満たさないチップの割合が10%以上あることが分かった。また、2024年の11月ごろにSLDO試験の12パラメータのうち、8つのパラメータの基準値が変更された。この変更は、試験量産の結果やシミュレーション等を踏まえてモジュールの性能を損ねない範囲で行われ、8つのうち6つのパラメータにおいては、passチップの割合の増加が見られた。しかし、残り2つのパラメータに関しては、基準値変更の影響が見られなかったため、今後の基準値の定義については、綿密に議論を行う必要があると考えられる。また、試験量産の結果から、failとなったチップが同一モジュールの他のチップに悪影響を及ぼしていると考えられる。特に、電源電流に関するSLDO IINA、IINDというパラメータに関する試験において、failと判定されたチップが他のチップに及ぼしている影響には注意が必要である。以上を踏まえ、本量産に向けて、歩留まりを確保する方法を用意する。

今後の展望としては、読み出し試験の結果解析を踏まえ、基準値を満たしたモジュールの割合が多いパラメータとそうでないパラメータが、そういった結果を出力した理由を特定し、本量産において、fail チップの割合を減らす方法を考える。SLDO パラメータ群以外についても、現在の試験で用いられている基準値や試験方法が妥当であるかを検証し、本量産で高効率、高精度で試験を行う手法について考察する。また、特定のパラメータ間の相関から、それらの間に何らかの因果関係があると考えられる。そのため、複数のパラメータで基準値外の結果を出力したチップについても、その原因を取り除けば、結果が改善する可能性がある。したがって、不良チップにおける問題点の原因を推定するための手法を検討する。加えて、本研究で調べた事項以外の情報を結果解析から得ることが今後の課題となっている。HL-LHC実験に実装するモジュールが揃うまでは今後も本量産は続くため、さらに多くの読み出し試験のデータをもとに、引き続き結果解析を行うことがモジュールの高品質化にとって重要であると考える。

## 8 考察

HL-LHC実験に向けた、ITkピクセルモジュールの量産において、電気回路読み出し試験の結果解析を行った。その結果、多くのパラメータにおいて、基準値から外れた値を出力するチップが見られた。これらのチップの増加は、モジュールの最初の読み出し試験においては小さかった欠陥が、品質管理試験の過程において、問題を拡大しつつ、他のチップに悪影響を及ぼしていることが原因であると考えられる。電源電流に関するパラメータにおいて fail と判定されたチップについては、他のパラメータでの試験においても fail と判定されることが多い傾向が見られる。よって、特に SLDO パラメータで fail となったチップの問題が同一モジュール上の他のチップに波及していると考えられる。そのため、今後の ITk の本量産の高品質化を目指すために、基準値の再定義などの読み出し試験の厳格化が必要である。また、高効率化のために、試験中での確認事項を定め、それを満たさなかったモジュールを分別する等の措置も有効であると考える。ただし、これまでに電気回路読み出し試験の全ての試験を完全に合格したモジュールは存在しないため、今後の量産に向けた試験の改善は注意して行う必要がある。

### 謝辞

まず、本研究を行うにあたり、非常に多くの方にご助力、ご指導いただきました。この場を借りて謝辞を述べさせていただきます。本当にありがとうございました。

初めに、指導教員である寄田浩平教授に感謝申し上げます。3年間という長い間研究指導をしていただきありがとうございました。毎週のグループミーティングにおいて、研究活動の方針についてアドバイスをいただくことで、目標をこまめに更新しつつ研究に取り組むことが出来ました。

また、田中雅士主席研究員にもお世話になりました。研究室内のグループこそ異なりましたが、中間発表を 始めとした研究発表の場でご指摘いただいた点は、非常に参考になりました。ありがとうございました。

坂本敦子秘書には、出張時や日々の事務手続きにおいて大変お世話になりました。研究室の雰囲気をしばしば和ませていただき、とても救いになりました。ありがとうございました。

また、ATLAS JAPAN グループで ITk ピクセルモジュール量産に関わっている方々にも大変お世話になりました。KEK の外川学様、生出秀幸様には、研究の方針を決める上で大きな助けとなっていただき、感謝申し上げます。特に、筑波大学の廣瀬茂輝様には、定期的に行われる ITk ピクセルモジュール QC データ解析ミーティングにおいて、実際に研究内容の指導に当たっていただきました。ハヤシレピックでの ITk 量産の現地シフトでは、ITk グループ全体のスタッフや学生の皆様にお世話になりました。また、ハヤシレピックの皆様にも量産のためのサイトをご用意いただいたことに対する感謝を述べたいと思います。皆様のご協力なくして、この研究は進められなかったと思います。本当にありがとうございました。

加えて、研究室の皆様に感謝を申し上げます。特に同期で同じグループの吉田君、荒川君には、さまざまな刺激を受けながら研究を進めることができました。いろいろなことを気軽に話すことができる同期の存在は大きな助けになりました。ありがとうございました。

最後に、金銭面、精神面ともに大きな支えとなってくれた両親に感謝したいと思います。本当にありがとう ございました。

### 参考文献

- [1] 国立大学附置研究所・センター会議, 東京大学素粒子物理国際研究センター, http://shochou-kaigi.org/interview/interview\_32/

- [2] The ATLAS Collaboration et al, The ATLAS Experiment at the CERN Large Hadron Collider, 2008, https://iopscience.iop.org/article/10.1088/1748-0221/3/08/S08003/pdf

- [3] CERN, The Inner Detector, https://atlas.cern/Discover/Detector/Inner-Detector

- [4] CERN, Keeping the ATLAS Inner Detector in perfect alignment, https://atlas.cern/updates/experiment-briefing/inner-detector-alignment

- [5] CERN, ATLAS Tile calorimeter calibration and monitoring systems, http://cds.cern.ch/record/2629424/plots

- [6] CERN, Schematic of the ATLAS Muon Spectrometer, https://atlas.cern/node/36981

- [7] ATLAS Collaboration, ATLAS Level-1 Endcap Muon Trigger for Run 3, https://cds.cern.ch/record/2709553/files/10.1051\_epjconf\_202024501002.pdf

- [8] Center for Particle Physics Siegen, ATLAS ITk, https://www.hep.physik.uni-siegen.de/research/atlas/atlas-itk

- [9] CERN, The HL-LHC project, https://hilumilhc.web.cern.ch/content/hl-lhc-project

- [10] SEMANTIC SCHOLAR, The ATLAS ITk Strip Detector System for the Phase-II LHC Upgrade, https://www.semanticscholar.org/paper/The-ATLAS-ITk-Strip-Detector-System-for-the-LHC-Wonsak/675979af0dc8ef2e9410b4b79fb7e5cc5fbf7f7e

- [11] Lingxin Meng, On behalf of the ATLAS ITk Pixel Collaboration, 2021, https://indico.cern.ch/event/995633/contributions/4259523/attachments/2210795/3741492/ 20210318\_LCWS\_ITkPixel\_lmeng.pdf

- [12] The ATLAS Collaboration, ATLAS Inner Tracker Pixel Detector Technical Design Report Technical Design Report, https://cds.cern.ch/record/2285585/files/ ATLAS-TDR-030.pdf

- [13] Leonardo Vannoli, ATLAS ITk Pixel Detector An Overview, 2023, https://cds.cern.ch/record/2857574/files/ATL-ITK-SLIDE-2023-123.pdf

[14] Lingxin Meng, Module and System Test Development for the Phase-2 ATLAS ITk Pixel Upgrade, 2020, https://www.researchgate.net/publication/340835355\_Module\_and\_System\_Test\_Development\_for \_the\_Phase-2\_ATLAS\_ITk\_Pixel\_Upgrade

- [15] 鈴木隆仁, HL-LHC ATLAS ピクセル検出器量産品質試験の温湿度管理システムの構築, 早稲田大学修士論文, 2022, http://www.kylab.sci.waseda.ac.jp/PUB/PAPER/MasterThesis/2021\_TakahitoSuzuki.pdf

- [16] 宮本佳門, ATLAS 実験用新型シリコンピクセル検出器の冷却部組立手法の研究, 2022, https://epp.phys.kyushu-u.ac.jp/thesis/2023MasterMiyamoto.pdf

- [17] 廣瀬茂樹, ITkpix module text draft, https://gitlab.cern.ch/shhirose/itkpix-module-text-draft

- [18] 大島英里香, 高輝度 LHC 実験 ATLAS ピクセル検出器モジュールの品質試験に向けたデータ管理 用 GUI の開発, 東京都立大学, 2022, https://www-hep.phys.se.tmu.ac.jp/thesis/doc/2021-Mthesis-oshima.pdf

学籍番号: 5323A015-5

## 研究活動の不正行為 定義確認書

2025年 月27日

早稲田大学大学院先進理工学研究科長 殿

早稲田大学大学院先進理工学研究科 物理学及心用物理学 専攻 2年

本人氏名 小川 貴弘

(自署)

私は、裏面に記載のある研究活動の不正行為に関する定義を理解し、修士論文提出において、不正行為を一切行っていないことを誓約します。

なお、当該行為を行なうと、厳重な処分 (無期停学・当該学期成績無効・修士論文不合格等)を受けること、学位取得後であっても学位取消となることを十分に認識した上で、 論文を執筆しました。

## 研究倫理教育受講確認書

本人氏名 八八八 電子

私は、修士論文の執筆にあたり、以下の研究倫理教育を受講しました。

| <b>/</b> | GEC 設置科目「学術・研究公正概論 (生命・理工系)」 |   |

|----------|------------------------------|---|

|          | GEC 設置科目「研究倫理概論」             |   |

|          | 専攻設置科目 科目名(                  | ) |

|          | その他(                         | ) |

|          | ※受講前に指導教員を通じて専攻主任の承認を受けること。  |   |

| -        | ※受講証明を添付すること。                |   |

## 研究活動の不正行為(捏造、改ざん、盗用、剽窃)について

修士論文を作成するに当たっては、以下の点に十分留意してください。